IBASE SMARC-EVK1 User Manual

Page 89

Copyright © 2013 IBASE Technology Inc. All Rights Reserved.

63

IBASE Technology Inc.

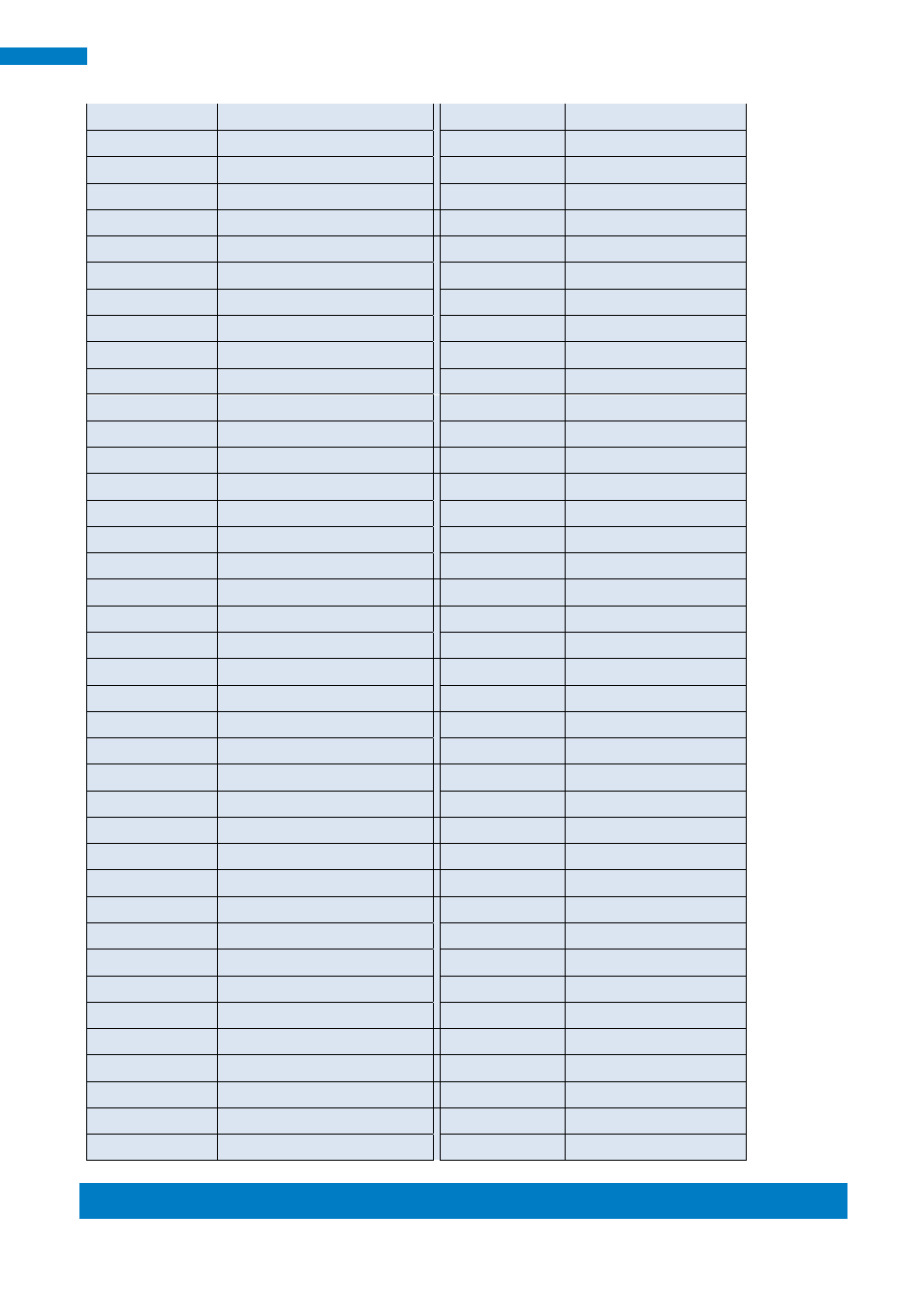

LVDS

LVDS0_TX3_N

W2

LVDS0_TX3_N

LVDS

LVDS0_TX3_P

W1

LVDS0_TX3_P

LVDS

LVDS0_CLK_N

V4

LVDS0_CLK_N

LVDS

LVDS0_CLK_P

V3

LVDS0_CLK_P

PCIe

PCIE_RST#

R1

GPIO_17

PCIe

PCIE_WAKE#

P3

CSI0_DATA_EN

PCIe

PCIE_CLK1_N

C7

CLK1_N

PCIe

PCIE_CLK1_P

D7

CLK1_P

PCIe

PCIE_RXM

B1

PCIE_RXM

PCIe

PCIE_RXP

B2

PCIE_RXP

PCIe

PCIE_TXM

A3

PCIE_TXM

PCIe

PCIE_TXP

B3

PCIE_TXP

SATA

SATA_RXP

B14

SATA_RXP

SATA

SATA_RXN

A14

SATA_RXM

SATA

SATA_TXN

B12

SATA_TXM

SATA

SATA_TXP

A12

SATA_TXP

I2C1

I2C1_SCL (I2C_PM)

N5

CSI0_DAT9

I2C1

I2C1_SDA (I2C_PM)

N6

CSI0_DAT8

I2C2

I2C2_SCL (I2C_CAM0)

U5

KEY_COL3

I2C2

I2C2_SDA (I2C_CAM0)

T7

KEY_ROW3

I2C3

I2C3_SCL (I2C_LCD)

R7

GPIO_3

I2C3

I2C3_SDA (I2C_LCD)

T3

GPIO_6

I2C4

I2C4_SCL (I2C_GP)

R3

GPIO_7

I2C4

I2C4_SDA (I2C_GP)

R5

GPIO_8

Toouch

Touch_INT#(GPIO_6)

B18

NANDF_D5

I2S

AUD3_TXC

N1

CSI0_DAT4

I2S

AUD3_TXD

P2

CSI0_DAT5

I2S

AUD3_TXFS

N4

CSI0_DAT6

I2S

AUD3_RXD

N3

CSI0_DAT7

I2S

HAD_RST# (GPIO_4)

D17

NANDF_D3

CLOCK

GPIO_0_CLKO

GPIO_0

CAN1

CAN1_TX

W6

KEY_COL2

CAN1

CAN1_RX

W4

KEY_ROW2