Layout recommendations, I2c interface, I2c signals – IBASE SMARC-EVK1 User Manual

Page 46: 1 signal impedance recommendation

20

SMARC Evaluation Kit

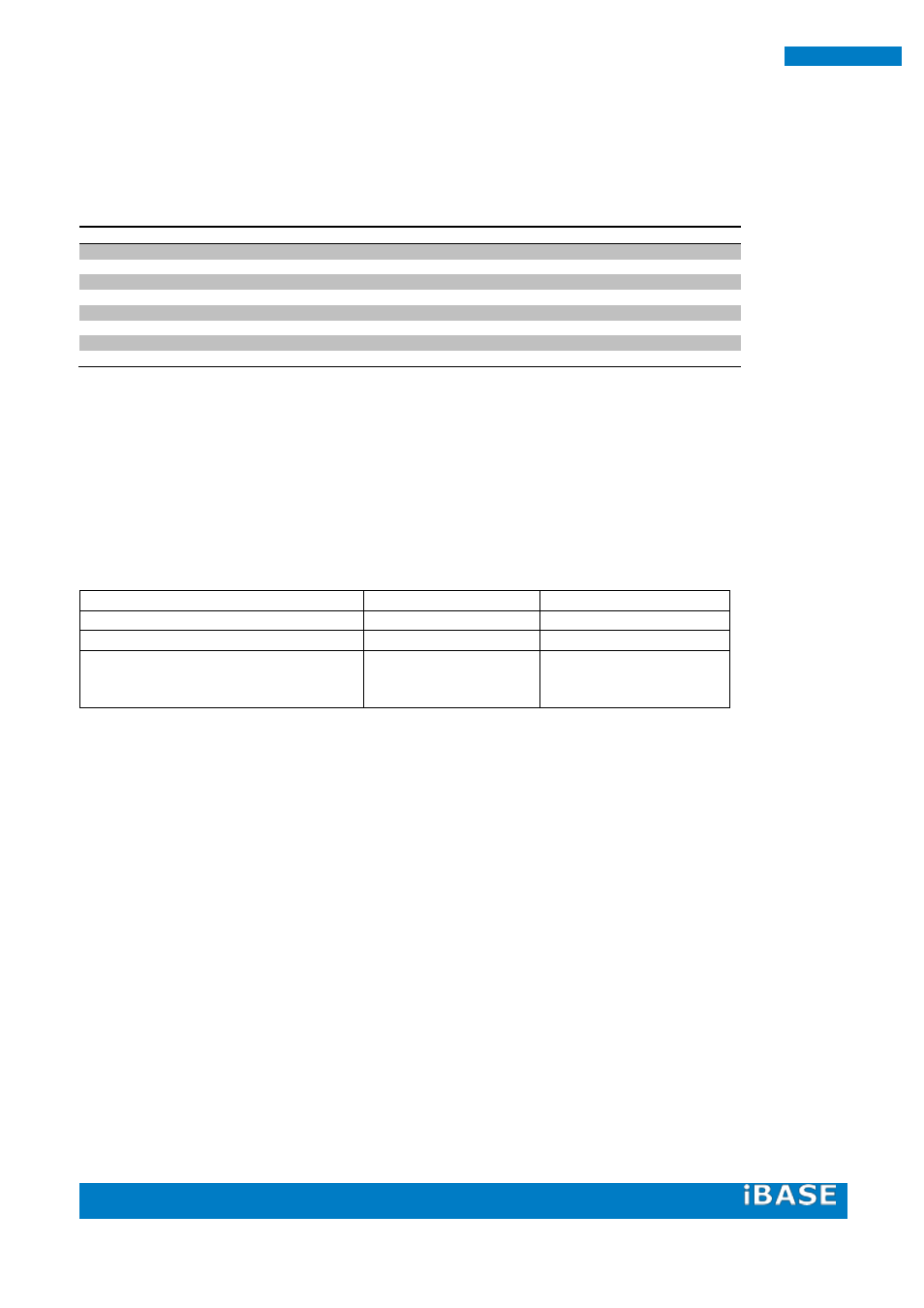

4.2.15. I2C Interface

I2C signals

Pin

Signal Name

I/O

Type

Power Rail

Description

P121

I2C1_SCL_1V8

O

OD

1.8V

I2C Clock signal for Audio CODEC

P122

I2C1_SDA_1V8

I/O

OD

1.8V

I2C Data signal for Audio CODEC

S5

I2C2_SCL

O

OD

3.3V

I2C Clock signal for Camera

S7

I2C2_SCL

I/O

OD

3.3V

I2C Data signal for Camera

S139

I2C3_SCL

O

OD

3.3V

I2C Clock signal for LCD Display

S140

I2C3_SCL

I/O

OD

3.3V

I2C Data signal for LCD Display

S48

I2C4_SCL

O

OD

3.3V

I2C Clock signal for PCI express

S49

I2C4_SCL

I/O

OD

3.3V

I2C Data signal for PCI express

4.3. Layout recommendations

1.1 Signal impedance recommendation

Signal Group

Impedance

Layout Tolerance (±)

All signals, unless specified

50 Ω Single End

10%

PCIe, USB Diff signals

90 Ω Differential

10%

Diff signals: LVDS, SATA, HDMI, DDR, MIPI

(CSI & DSI), MLB, PHY IC to Ethernet

Connector

100 Ω Differential

10%