I annex: post-codes – BECKHOFF CB2051 User Manual

Page 73

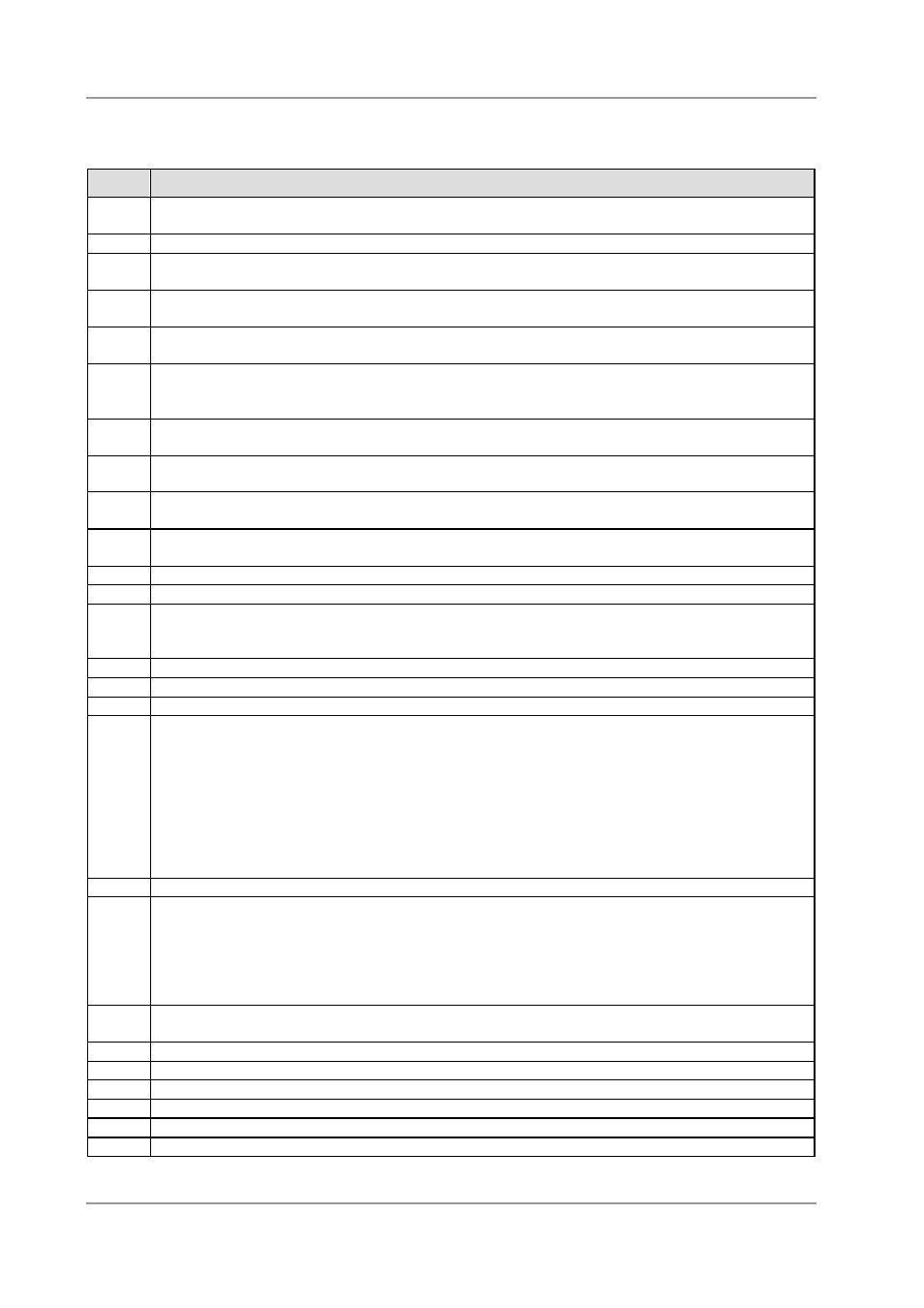

Annex: Post-Codes

Beckhoff New Automation Technology CB2051

page 73

I Annex: Post-Codes

Code

Description

01h

The Xgroup-program code is written in the random access memory from address 1000:0

onwards.

03h

Initialise Variable/Routine "Superio_Early_Init".

05h

1. Cancel display

2. Cancel CMOS error flag

07h

1. Cancel 8042 (keyboard controller) Interface Register

2. Initialising and self testing of 8042 (keyboard controller)

08h

1. Test of special keyboard controllers (Winbond 977 super I/O Chip-series).

2. Enabling of the keyboard-interface register

0Ah

1. Disabling of the PS/2 mouse interface (optional).

2. Auto-detection of the connectors for Keyboard and mouse, optional: swap of PS/2 mouse

ports and PS/2 interfaces.

0Eh

Test of the F000h-memory segment (Read/Write ability). In case of an error a signal will come

out of the loud speakers.

10h

Auto-detection of the flash-rom-type and loading of the suitable Read/Write program into the run

time memory segment F000 (it is required for ESCD-data & the DMI-pool-support).

12h

Interface-test of the CMOS RAM-logic (walking 1’s”-algorithm). Setting of the power status of

the real-time-clock (RTC), afterwards test of register overflow.

14h

Initialising of the chip-set with default values. They can be modified through a software

(MODBIN) by the OEM-customer.

16h

Initialise Variable/Routine "Early_Init_Onboard_Generator".

18h

CPU auto-detection (manufacturer, SMI type (Cyrix or Intel), CPU-class (586 or 686).

1Bh

Initialising if the interrupt pointer table. If nothing else is pretended, the hardware interrupts will

point on “SPURIOUS_INT_HDLR and the software interrupts will point on

SPURIOUS_soft_HDLR.

1Dh

Initialise Variable/Routine EARLY_PM_INIT.

1Fh

Load the keyboard table (Notebooks)

21h

Initialising of the hardware power management (HPM) (Notebooks)

23h

1. Test the validity of the RTC-values (Example: “5Ah” is an invalid value for an RTC-minute).

2. Load the CMOS-values into the BIOS Stack. Default-values are loaded if CMOS-checksum

errors occur.

3. Preparing of the BIOS ‘resource map’ for the PCI & plug and play configuration. If ESCD is

valid, take into consideration the ESCD’s legacy information.

4. Initialise the onboard clock generator. Clock circuit at non-used PCI- and DIMM slots.

5. First initialising of PCI-devices: assign PCI-bus numbers - alot memory- & I/O resources -

search for functional VGA-controllers and VGA-BIOS and copy the latter into memory segment

C000:0 (Video ROM Shadow).

27h

Initialise cache memory for INT 09

29h

1. Program the CPU (internal MTRR at P6 and PII) for the first memory address range (0-640K).

2. Initialising of the APIC at CPUs of the Pentium-class.

3. Program the chip-set according to the settings of the CMOS-set-up (Example: Onboard IDE-

controller).

4. Measuring of the CPU clock speed.

5. Initialise the video BIOS.

2Dh

1. Initialise the “Multi-Language”-function of the BIOS

2. Soft copy, e.g. Award-Logo, CPU-type and CPU clock speed…

33h

Keyboard-reset (except super I/O chips of the Winbond 977 series)

3Ch

Test the 8254 (timer device)

3Eh

Test the interrupt Mask bits of IRQ-channel 1 of the interrupt controller 8259.

40h

Test the interrupt Mask bits of IRQ-channel 2 of the interrupt controller 8259

43h

Testing the function of the interrupt controller (8259).

47h

Initialise EISA slot (if existent).