BECKHOFF CB2051 User Manual

Page 17

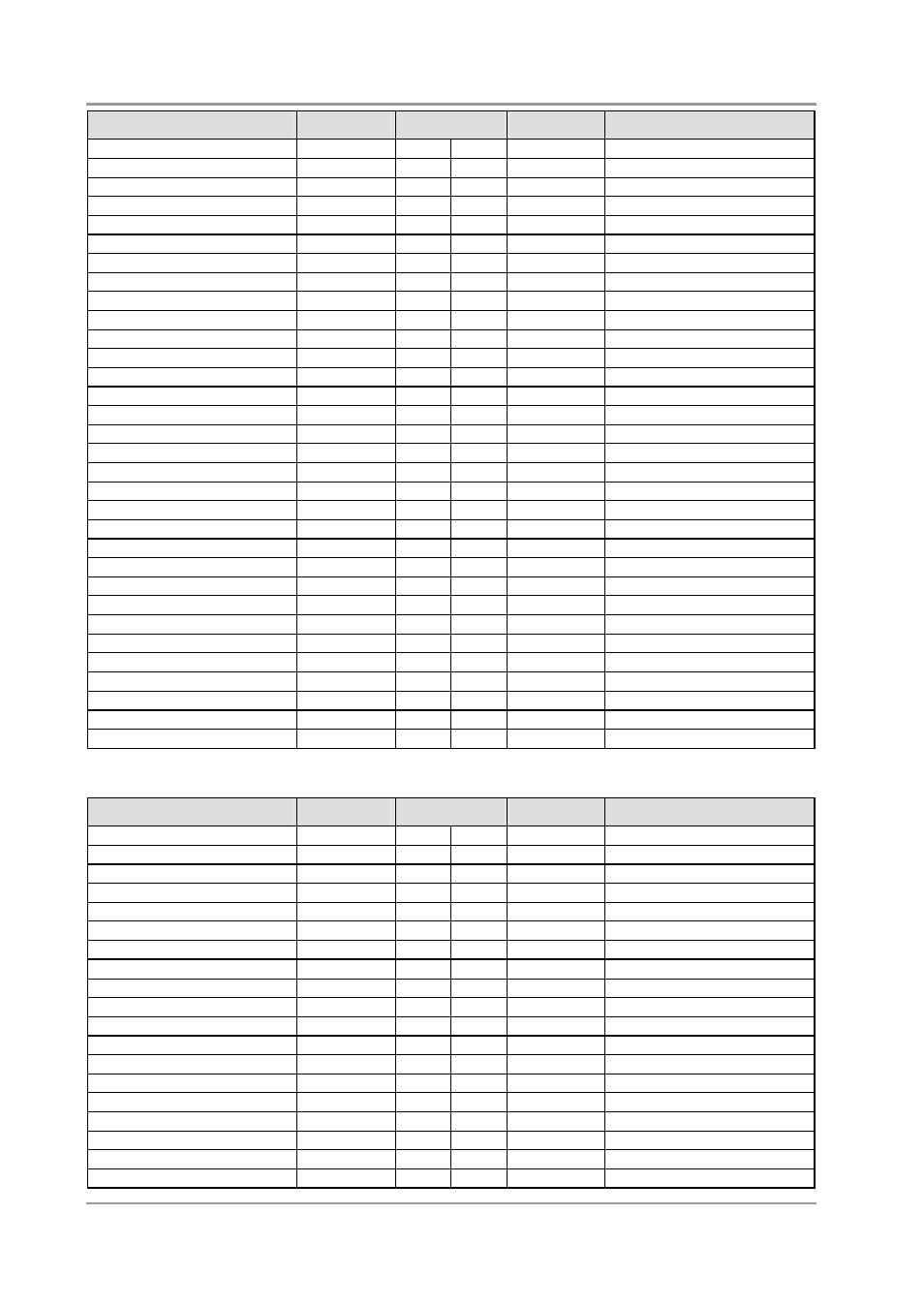

PISA Slot

Chapter: Connectors

Beckhoff New Automation Technology CB2051

page 17

Description

Name

Pin

Name

Description

system address 13

SA13

A18

B18

DRQ1

DMA request 1

system address 12

SA12

A19

B19

REFRESH# refresh

system address 11

SA11

A20

B20

SYSCLK

system clock

system address 10

SA10

A21

B21

IRQ7

interrupt request 7

system address 9

SA9

A22

B22

IRQ6

interrupt request 6

system address 8

SA8

A23

B23

IRQ5

interrupt request 5

system address 7

SA7

A24

B24

IRQ4

interrupt request 4

system address 6

SA6

A25

B25

IRQ3

interrupt request 3

system address 5

SA5

A26

B26

DACK2#

DMA acknowledge 2

system address 4

SA4

A27

B27

T/C

terminal count

system address 3

SA3

A28

B28

BALE

address latch enable

system address 2

SA2

A29

B29

VCC

5 volt supply

system address 1

SA1

A30

B30

OSC14

14.31818 MHz

system address 0

SA0

A31

B31

GND

ground

byte high enable

SBHE#

C1

D1

MEMCS16# memory chip select

latched address 23

LA23

C2

D2

IOCS16#

IO chip select

latched address 22

LA22

C3

D3

IRQ10

interrupt request 10

latched address 21

LA21

C4

D4

IRQ11

interrupt request 11

latched address 20

LA20

C5

D5

IRQ12

interrupt request 12

latched address 19

LA19

C6

D6

IRQ13

interrupt request 13

latched address 18

LA18

C7

D7

IRQ14

interrupt request 14

latched address 17

LA17

C8

D8

DACK0#

DMA acknowledge 0

memory read

MEMR#

C9

D9

DRQ0

DMA request 0

memory write

MEMW#

C10

D10

DACK5#

DMA acknowledge 5

system data 8

SD8

C11

D11

DRQ5

DMA request 5

system data 9

SD9

C12

D12

DACK6#

DMA acknowledge 6

system data 10

SD10

C13

D13

DRQ6

DMA request 6

system data 11

SD11

C14

D14

DACK7#

DMA acknowledge 7

system data 12

SD12

C15

D15

DRQ7

DMA request 7

system data 13

SD13

C16

D16

VCC

5 volt supply

system data 14

SD14

C17

D17

MASTER#

bus master

system data 15

SD15

C18

D18

GND

ground

Pinout "low row":

Description

Name

Pin

Name

Description

I2C clock

I2CLK

E1

F1

I2DAT

I2C data

ground

GND

E2

F2

GND

ground

interrupt B

INTB#

E3

F3

INTA#

interrupt A

interrupt D

INTD#

E4

F4

INTC#

interrupt C

5 volt supply

VCC

E5

F5

VCC

5 volt supply

coded

N/C

E6

F6

N/C

coded

5 volt supply

VCC

E7

F7

VIO

IO supply

PCI reset 2

PRST2#

E8

F8

PCLK2

PCI clock

grant 0

GNT0#

E9

F9

GND

ground

request 0

REQ0#

E10

F10

GNT1#

grant 1

ground

GND

E11

F11

GND

ground

PCI clock 1

PCLK1

E12

F12

REQ1#

request 1

ground

GND

E13

F13

AD31

address/data 31

address/data 30

AD30

E14

F14

AD29

address/data 29

request 2

REQ2#

E15

F15

PCLK3

PCI clock 3

coded

N/C

E16

F16

N/C

coded

grant 2

GNT2#

E17

F17

PCLK4

PCI clock 4

address/data 28

AD28

E18

F18

AD27

address/data 27

address/data 26

AD26

E19

F19

AD25

address/data 25