Appendix b: gpi/o programming guide, B: gpi/o p, Ppendix – NEXCOM NIFE 100 User Manual

Page 78: Rogramming, Uide

Copyright © 2015 NEXCOM International Co., Ltd. All Rights Reserved.

64

NIFE 100/101 User Manual

Appendix B: GPI/O Programming Guide

a

PPendIx

B: GPI/o P

roGrammInG

G

uIde

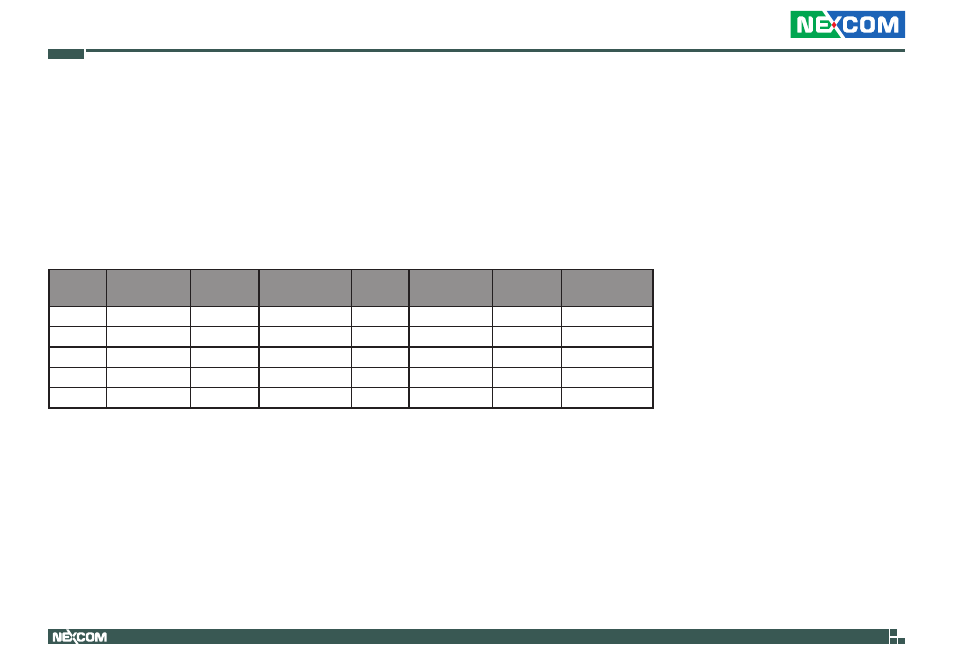

GPI/O (General Purpose Input/Output) pins are provided for custom system

design. This appendix provides definitions and its default setting for the ten

GPI/O pins in the NIFE 100/101 series. The pin definition is shown in the

following table:

Pin

GPI/O Mode

PowerOn

Default

Address

Pin

GPI/O Mode

PowerOn

Default

Address

1

VCC

-

-

2

GND

-

-

3

GPO0

Low

A03h (Bit6)

4

GPI0

High

A03h (Bit1)

5

GPO1

Low

A02h (Bit5)

6

GPI1

High

A05h (Bit5)

7

GPO2

Low

A07h (Bit0)

8

GPI2

High

A05h (Bit4)

9

GPO3

Low

A07h (Bit1)

10

GPI3

High

A00h (Bit1)

Control the GPO 0/1/2/3 level from I/O port A03h bit 6/ A02h bit 5 A07h bit 0/ A07h bit 1.

The bit is Set/Clear indicated output High/Low.