5 address maps, 1 memory address map, Address maps – ADLINK CoreExpress-ECO2 User Manual

Page 27: Memory address map

TME-CEM-ECO2-Rev0V4.doc

Rev 0.4

Page 23

5 Address Maps

This section describes the layout of the CPU memory and I/O address spaces.

Note Depending on enabled or disabled functions in the BIOS, other or

more resources may be used

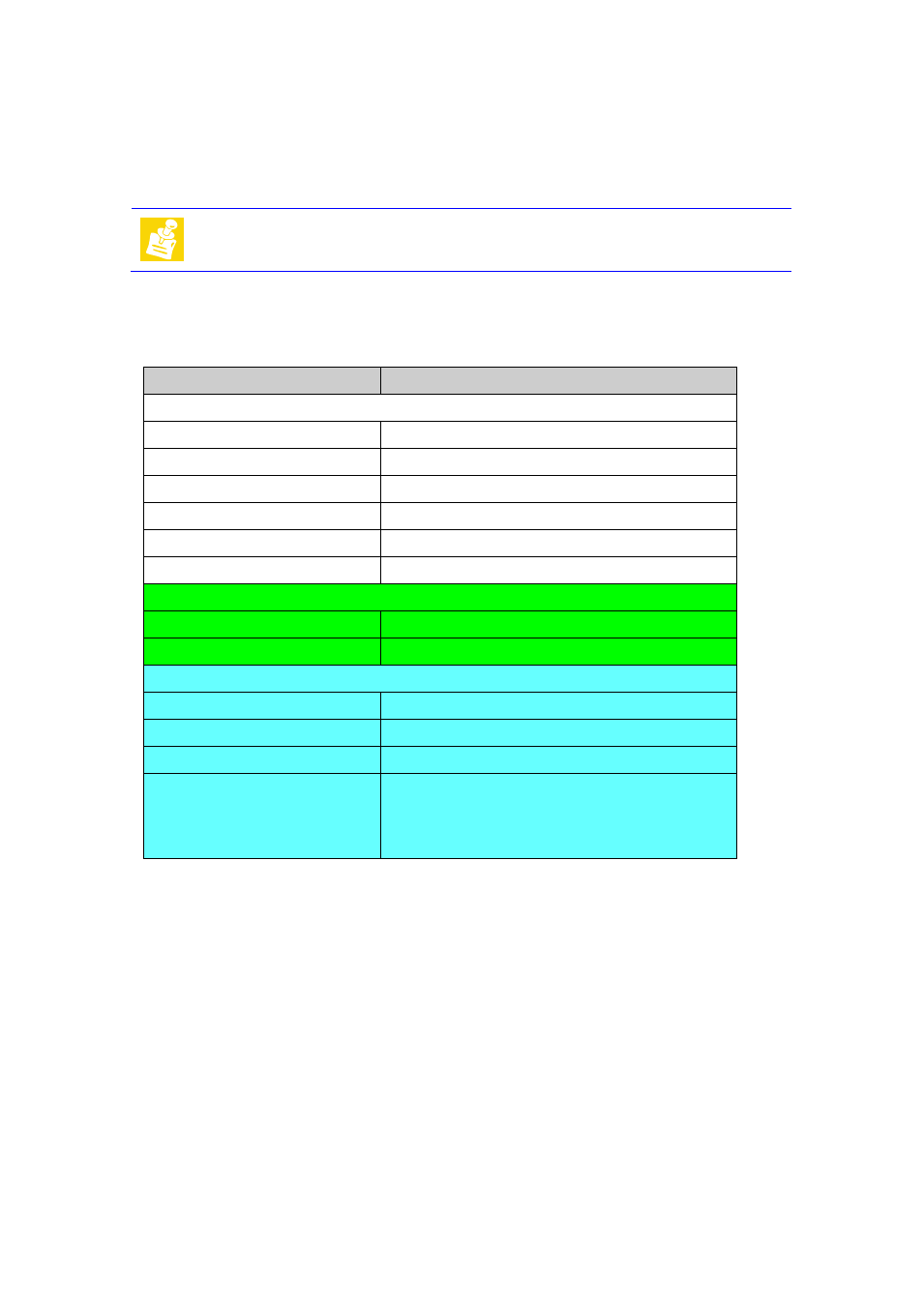

5.1 Memory Address Map

Address Range (Hex)

Description

Legacy Address Range (0 to 1 MB)

00000000 – 0009FFFF

DOS_DRAM

000A0000 – 000DFFFF

Legacy Video (VGA)

000E0000 – 000EFFFF

PAM

000F0000 – 000FFFFF

PAM

000F0000 – 000FFFFF

BIOS (LPC)

000E0000 – 000FFFFF

LPC (Provided PAM is not enabled)

Main Memory (1MB to TOM)

Variable – Variable

TSEG

Variable – Variable

Graphics

PCI Configuration Space (2GB to 4GB)

FEC00000 – FEC00040

IOxAPIC

FED00000 – FED003FF

HPET (High Performance Event Timer)

FED04000 – FED4BFFF

TPM1.2 (LPC)

FFC00000 – FFFFFFFF

High BIOS (The Chipset Microcode (CMC) base

address lives within the LPC space and

consumes 64 kB of space. Make sure to avoid

using the same starting address for other

LPC devices in the system. )