4 com express board-to-board connectors, Com express board-to-board connectors, Signals and pinout for: basic form factor, type 2 – ADLINK Express-BASE User Manual

Page 13: C d a b, Page 13 express-base user’s manual

Page 13

Express-BASE User’s Manual

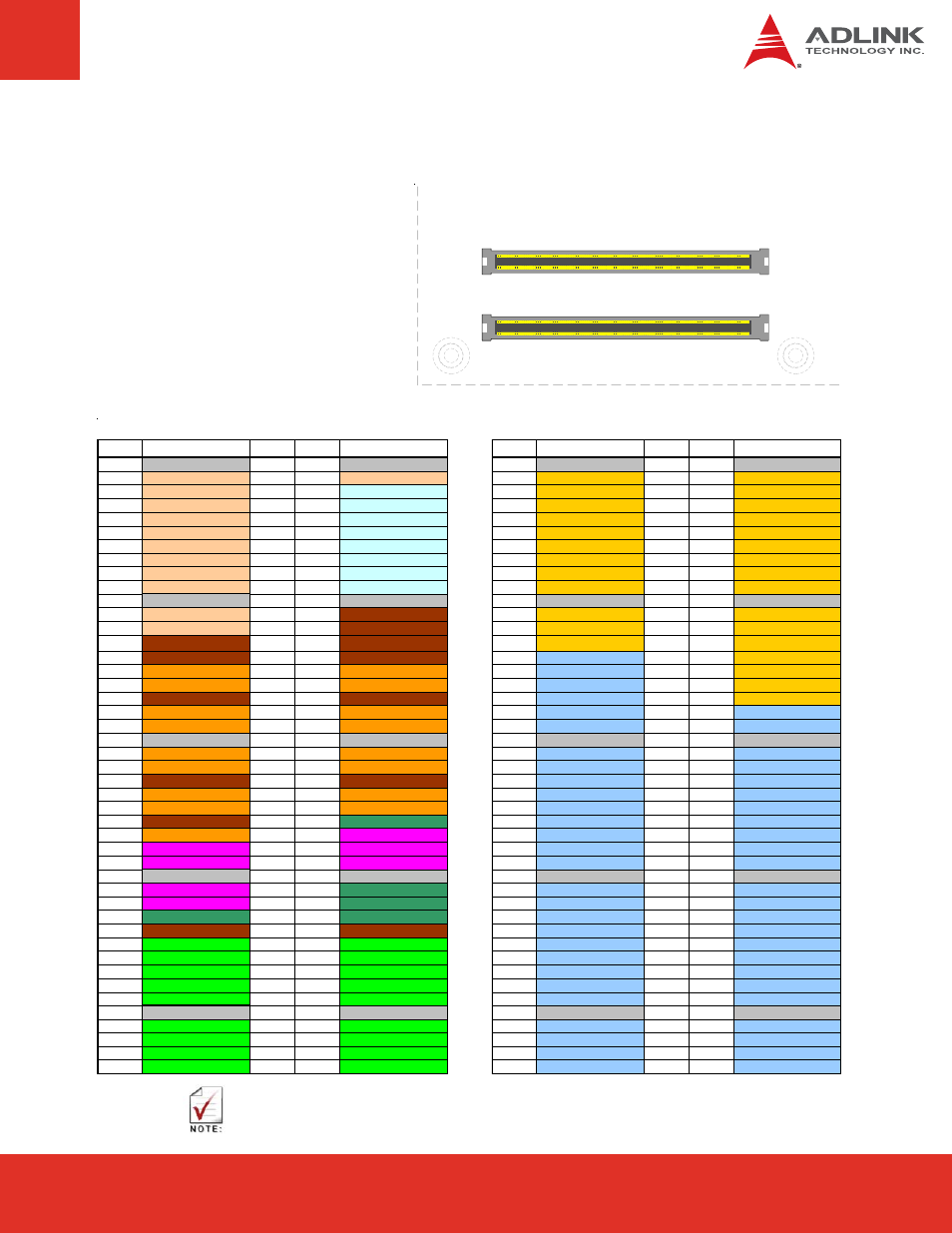

6.4 COM Express Board-to-Board Connectors

Signals and Pinout for:

Basic form factor, Type 2.

C D

A B

A1

B1

C1

D1

A110

B110

C110

D110

Pin No. Pin Name

Pin No. Pin Name

Pin No. Pin Name

Pin No. Pin Name

A1

GND (FIXED)

B1

GND (FIXED)

C1

GND FIXED)

D1

GND FIXED)

A2

GBE0_MDI3-

B2

GBE0_ACT#

C2

IDE_D7

D2

IDE_D5

A3

GBE0_MDI3+

B3

LPC_FRAME#

C3

IDE_D6

D3

IDE_D10

A4

GBE0_LINK100#

B4

LPC_AD0

C4

IDE_D3

D4

IDE_D11

A5

GBE0_LINK1000#

B5

LPC_AD1

C5

IDE_D15

D5

IDE_D12

A6

GBE0_MDI2-

B6

LPC_AD2

C6

IDE_D8

D6

IDE_D4

A7

GBE0_MDI2+

B7

LPC_AD3

C7

IDE_D9

D7

IDE_D0

A8

GBE0_LINK#

B8

LPC_DRQ0#

C8

IDE_D2

D8

IDE_REQ

A9

GBE0_MDI1-

B9

LPC_DRQ1#

C9

IDE_D13

D9

IDE_IOW#

A10

GBE0_MDI1+

B10

LPC_CLK

C10

IDE_D1

D10

IDE_ACK#

A11

GND (FIXED)

B11

GND (FIXED)

C11

GND (FIXED)

D11

GND (FIXED)

A12

GBE0_MDI0-

B12

PWRBTN#

C12

IDE_D14

D12

IDE_IRQ

A13

GBE0_MDI0+

B13

SMB_CK

C13

IDE_IORDY

D13

IDE_A0

A14

GBE0_CTREF

B14

SMB_DAT

C14

IDE_IOR#

D14

IDE_A1

A15

SUS_S3#

B15

SMB_ALERT#

C15

PCI_PME#

D15

IDE_A2

A16

SATA0_TX+

B16

SATA1_TX+

C16

PCI_GNT2#

D16

IDE_CS1#

A17

SATA0_TX-

B17

SATA1_TX-

C17

PCI_REQ2#

D17

IDE_CS3#

A18

SUS_S4#

B18

SUS_STAT#

C18

PCI_GNT1#

D18

IDE_RESET#

A19

SATA0_RX+

B19

SATA1_RX+

C19

PCI_REQ1#

D19

PCI_GNT3#

A20

SATA0_RX-

B20

SATA1_RX-

C20

PCI_GNT0#

D20

PCI_REQ3#

A21

GND (FIXED)

B21

GND (FIXED)

C21

GND (FIXED)

D21

GND (FIXED)

A22

SATA2_TX+

B22

SATA3_TX+

C22

PCI_REQ0#

D22

PCI_AD1

A23

SATA2_TX-

B23

SATA3_TX-

C23

PCI_RESET#

D23

PCI_AD3

A24

SUS_S5#

B24

PWR_OK

C24

PCI_AD0

D24

PCI_AD5

A25

SATA2_RX+

B25

SATA3_RX+

C25

PCI_AD2

D25

PCI_AD7

A26

SATA2_RX-

B26

SATA3_RX-

C26

PCI_AD4

D26

PCI_C/BE0#

A27

BATLOW#

B27

WDT

C27

PCI_AD6

D27

PCI_AD9

A28

(S)ATA_ACT#

B28

AC/HDA_SDIN2

C28

PCI_AD8

D28

PCI_AD11

A29

AC/HDA_SYNC

B29

AC/HDA_SDIN1

C29

PCI_AD10

D29

PCI_AD13

A30

AC/HDA_RST#

B30

AC/HDA_SDIN0

C30

PCI_AD12

D30

PCI_AD15

A31

GND (FIXED)

B31

GND (FIXED)

C31

GND (FIXED)

D31

GND (FIXED)

A32

AC/HDA_BITCLK

B32

SPKR

C32

PCI_AD14

D32

PCI_PAR

A33

AC/HDA_SDOUT

B33

I2C_CK

C33

PCI_C/BE1#

D33

PCI_SERR#

A34

BIOS_DIS0#

B34

I2C_DAT

C34

PCI_PERR#

D34

PCI_STOP#

A35

THRMTRIP#

B35

THRM#

C35

PCI_LOCK#

D35

PCI_TRDY#

A36

USB6-

B36

USB7-

C36

PCI_DEVSEL#

D36

PCI_FRAME#

A37

USB6+

B37

USB7+

C37

PCI_IRDY#

D37

PCI_AD16

A38

USB_6_7_OC#

B38

USB_4_5_OC#

C38

PCI_C/BE2#

D38

PCI_AD18

A39

USB4-

B39

USB5-

C39

PCI_AD17

D39

PCI_AD20

A40

USB4+

B40

USB5+

C40

PCI_AD19

D40

PCI_AD22

A41

GND (FIXED)

B41

GND (FIXED)

C41

GND (FIXED)

D41

GND (FIXED)

A42

USB2-

B42

USB3-

C42

PCI_AD21

D42

PCI_AD24

A43

USB2+

B43

USB3+

C43

PCI_AD23

D43

PCI_AD26

A44

USB_2_3_OC#

B44

USB_0_1_OC#

C44

PCI_C/BE3#

D44

PCI_AD28

A45

USB0-

B45

USB1-

C45

PCI_AD25

D45

PCI_AD30

Row A

Row B

Row C

Row D

Pin definitions that are new for COM.0 Rev. 2.0 are highlighted in bold.