2 bypass control priority, Bypass control priority – ADLINK PMC-8246 User Manual

Page 25

Programming Information

13

PMC-8246

WDT Reload

When WDT is reload, the circuit will load the WDT value from

either WDT_VP[1:0] or WDV_VS[1:0] dependent on the control

modes setting.

WDT Time Out Value Seting

3.2

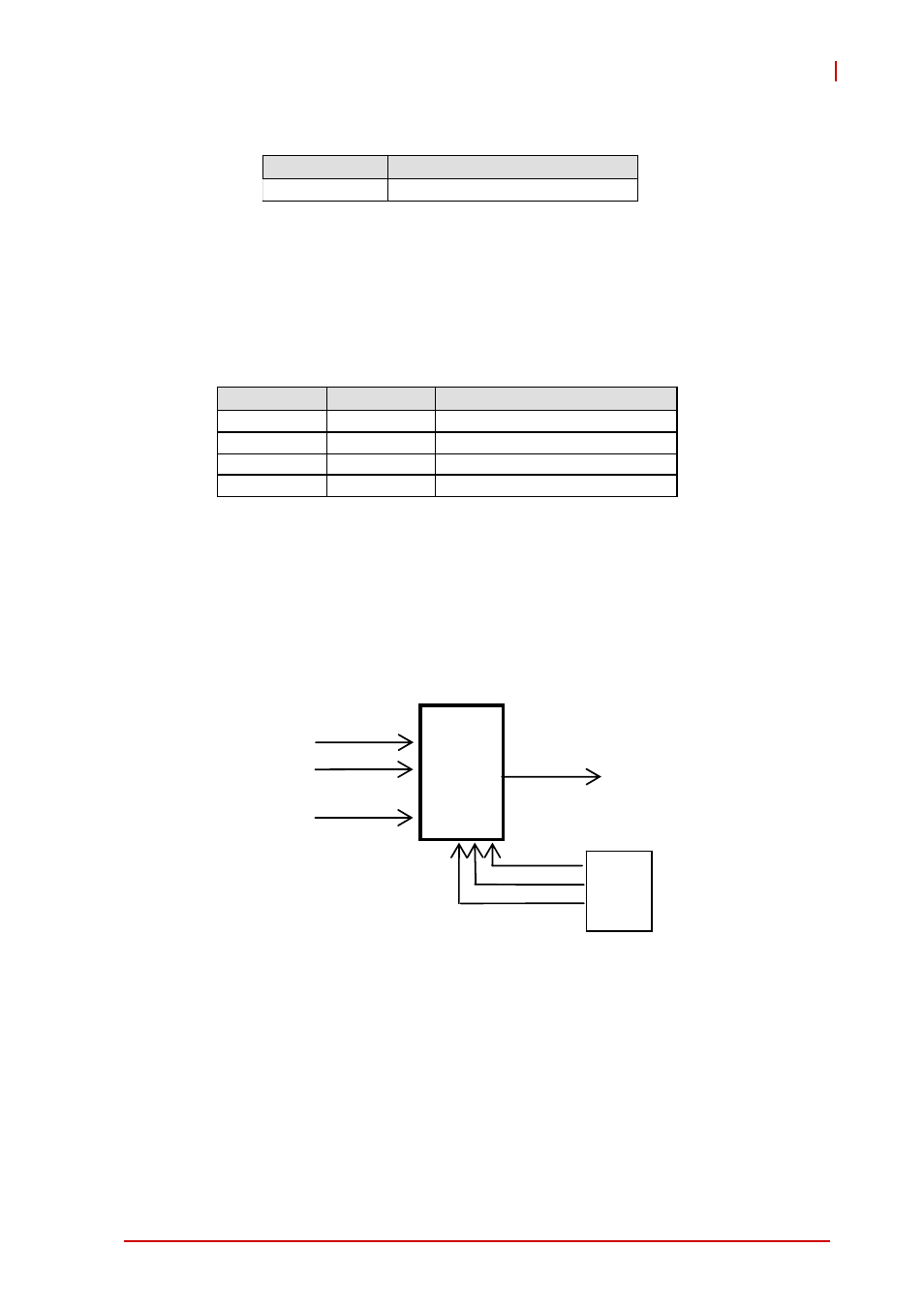

Bypass Control Priority

The relay array is controlled by reset, WDT time out, bypass con-

trol mode bits, and external settings from the header. Please refer

to the following block diagram.

WDT_RL

Functions

0 -> 1 -> 0

Reload WDT to avoid timeout

WDT_VP1 WDT_VP0

WDT time out value

0 0

1

second

Power On Default

0 1

2

seconds

1 0

4

seconds

1 1

8

seconds

WDT

Time Out

Bypass

Control

Logic

MODE[0:1]

Control

Relay

BYPASS

NORMAL

PONSTS

PCI_RESET

SWX1

See also other documents in the category ADLINK Hardware:

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (83 pages)

- cPCI-7300 (82 pages)