ADLINK PMC-8246 User Manual

Page 24

12

Programming Information

SDP Registers Definition

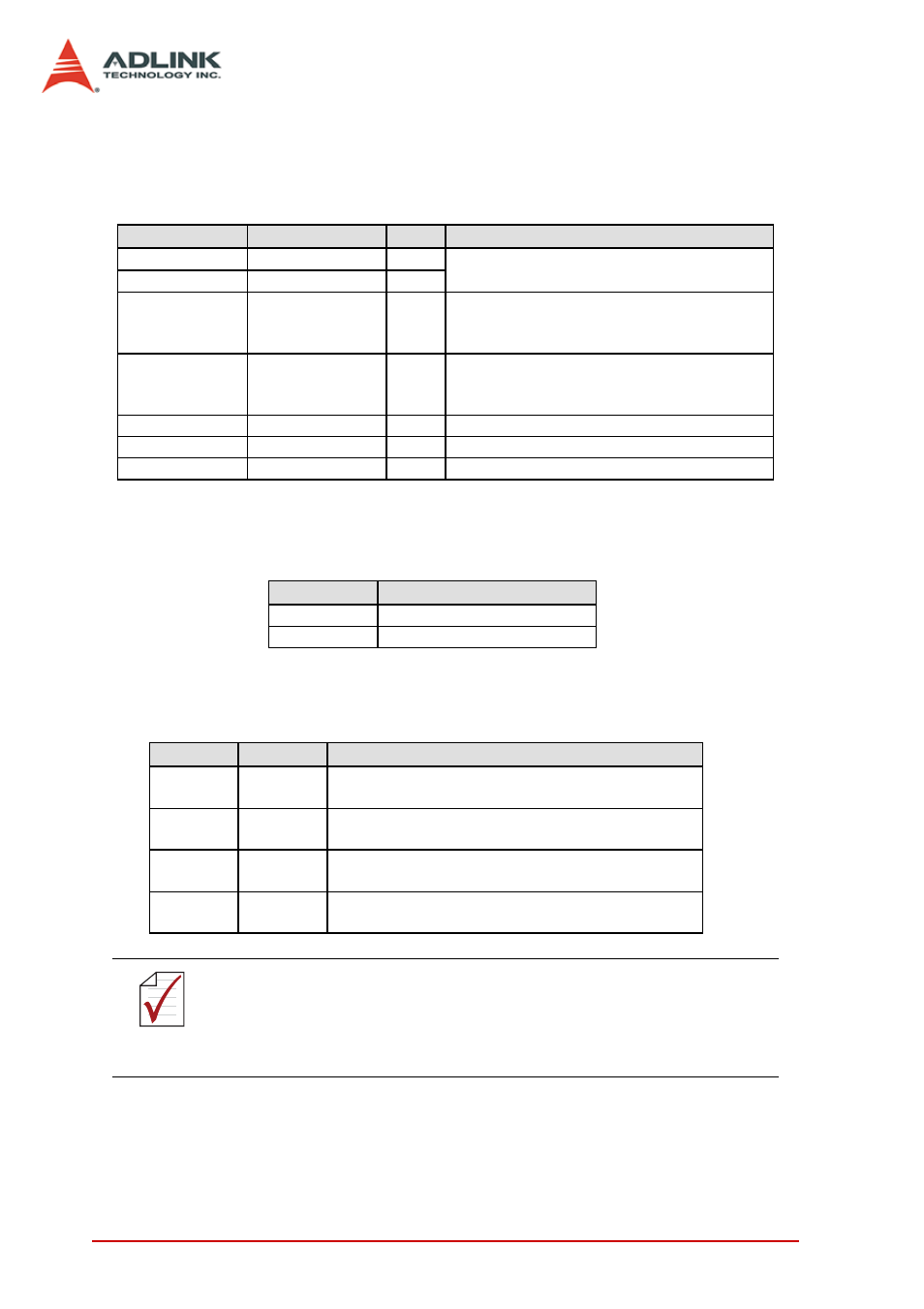

The bits in SDP registers are all readable and writable. The follow-

ing table shows the register definition.

WDT Enable

Bypass Control Mode

NOTE:

NOTE:

Note 1: If the relay array is forced to Normal State by settings in

the Control Switch (SWX1), then this setting is void.

Note 2: If the relay array is forced to Bypass State by settings in

the Control Switch (SWX1), then this setting is void.

SPD Bit

Name

R/W

Description

SDPB0 MODE0

RW

SDPB1 MODE1

RW

Bypass control mode bit 0 and 1

SDPB6 Bypass

Status

R

Bypass status read back

0:

Bypass

1:

Normal

SDPB7 WDT

Status

R

WDT status read back

0: WDT running or stop

1: WDT Time Out

SDPA0 WDT_CTRL

RW

WDT

control

bit

SDPA1

WDT_RL

RW Reload WDT to avoid timeout

SDPA6

WDT_VP0

RW WDT time out value bit 0 and 1

WDT_EN Functions

0

WDT is disabled.

Power On Default

1 WDT

is

enabled.

MODE0 MODE1

Functions

0

0

No enforcement. Set WDT reload from the

switch setting WDT_VS[1:0]

Power On

Default

0 1

No enforcement. Set WDT reload from the

programmable WDT_VP[1:0]

1 0

Disable WDT, enforce relay array in Bypass

State (1)

1 1

Disable WDT, enforce relay array in Normal

State (2)