3 watchdog timer, 1 watchdog timer setting – Acrosser AR-B9622 User Manual

Page 37

AR-B9622 User¡

¦s Guide

5-3

5.3 WATCHDOG TIMER

This section describes how to use the Watchdog Timer, disabled, enabled, and trigger.

The AR-B9622 is equipped with a programmable time-out period watchdog timer. User can use the program to

enable the watchdog timer. Once you have enabled the watchdog timer, the program should trigger it every time

before it times out. If your program fails to trigger or disable this timer before it times out because of system hang-

up, it will generate a reset signal to reset the system. The time-out period can be programmed to be

30.5£ g

seconds to 512 seconds.

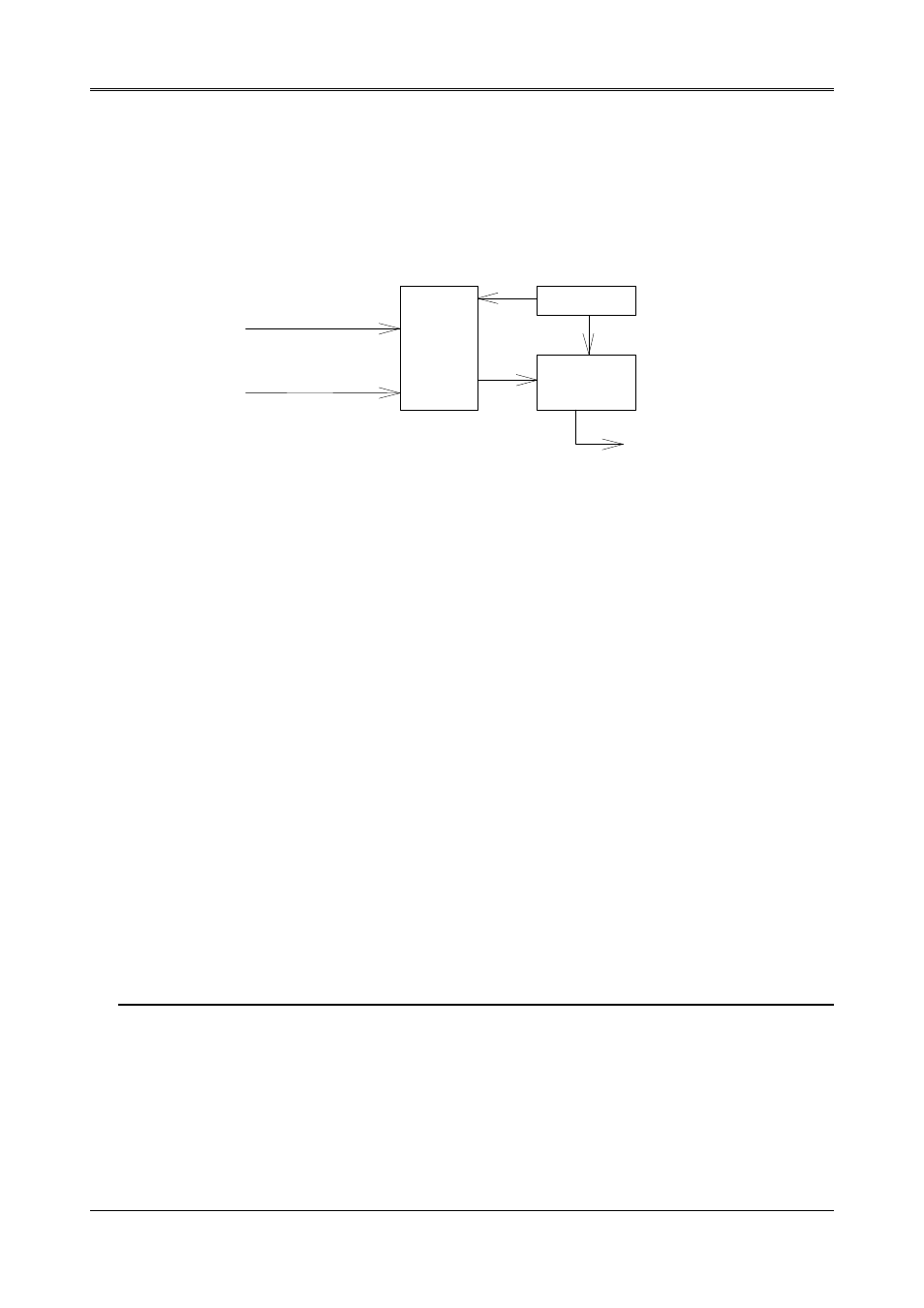

Watchdog

Register

Time Base

Counter

and

Compartor

Software Program

Enable and Trigger

Write and Trigger

RESET

Figure 5-1 Watchdog Block Diagram

5.3.1 Watchdog Timer Setting

The watchdog timer is a circuit that may be used from your program software to detect crashes or hang-ups. The

watchdog timer is automatically disabled after reset.

Once you have enabled the watchdog timer, your program must trigger the watchdog timer every time before it

times-out. After you trigger the watchdog timer, it will be set to zero and start to count again. If your program fails

to trigger the watchdog timer before time-out, it will generate a reset pulse to reset the system or trigger the IRQ15

signal to tell your program that the watchdog is times out.

Watchdog timer -INDEX 39H, 3AH, 3BH

3Bh

3Ah

39h

D7

0

D7

0

D7

0

Counter [MSB …LSB]

For example

INDEX

3Bh 3Ah 39h

00h 00h 01h 30.5 £ gsec

--

--

02h 61 £ gsec

00h 01h 00h 7.8 m sec

00h 02h 00h 15.6 m sec

01h 00h 00h 2 sec

02h 00h 00h 4 sec

FFh FFh FFh 512 sec

If you want to generate IRQ15 signal to warn your program when watchdog times out, the following table listed the

relation of timer factors between time-out period. And if you use the IRQ15 signal to warn your program when

watchdog timer out, please enter the BIOS Setup the

NOTE: 1. If you program the watchdog to generate IRQ15 signal when it times out, you should initial IRQ15

interrupt vector and enable the second interrupt controller (8259 PIC) in order to enable CPU to process

this interrupt. An interrupt service routine is required too.

2. Before you initial the interrupt vector of IRQ15 and enable the PIC, please enable the watchdog timer

previously, otherwise the watchdog timer will generate an interrupt at the time watchdog timer is

enabled.