3 hard disk (ide) connector (cn3) – Acrosser AR-B9622 User Manual

Page 23

AR-B9622 User¡

¦s Guide

3-5

Name

Description

-MASTER [Input]

The MASTER is the signal from the I/O processor which

gains control as the master and should be held low for a

maximum of 15 microseconds or system memory may be

lost due to the lack of refresh

-MEMCS16

[Input, Open collector]

The Memory Chip Select 16 indicates that the present

data transfer is a 1-wait state, 16-bit data memory

operation

-IOCS16

[Input, Open collector]

The I/O Chip Select 16 indicates that the present data

transfer is a 1-wait state, 16-bit data I/O operation

OSC [Output]

The Oscillator is a 14.31818 MHz signal

-ZWS

[Input, Open collector]

The Zero Wait State indicates to the microprocessor that

the present bus cycle can be completed without inserting

additional wait cycle

Table 3-1 PC/104 ISA Pin Assignment

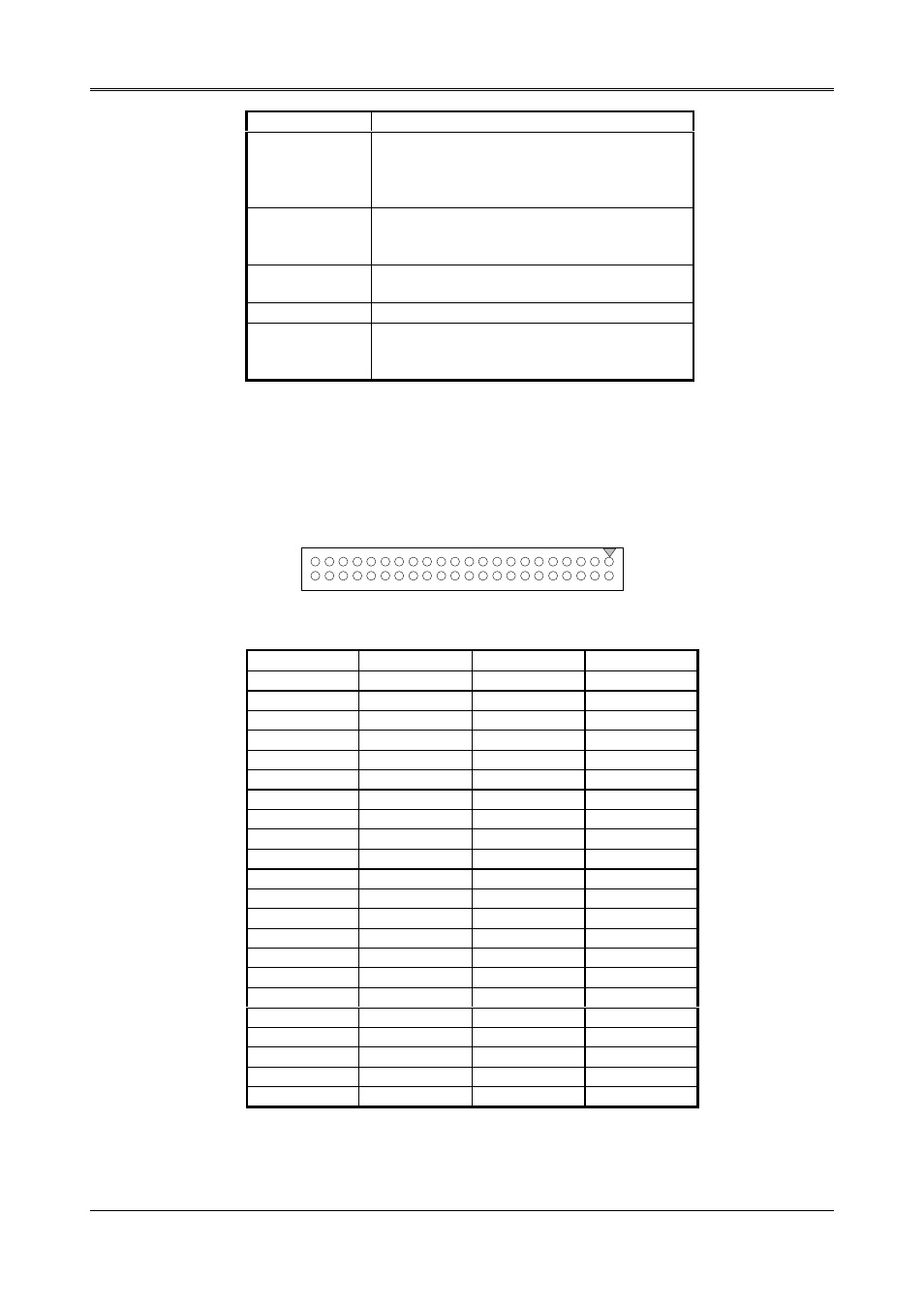

3.2.3 Hard Disk (IDE) Connector (CN3)

A 44-pin header type connector (CN3) is provided to interface with up to two embedded hard disk drives (IDE AT

bus). This interface, through a 44-pin cable, allows the user to connect up to two drives in a “daisy chain” fashion.

To enable or disable the hard disk controller, please use BIOS Setup program to select. The following table

illustrates the pin assignments of the hard disk drive’ s 40-pin connector.

1

2

44

43

Figure 3-6 CN3: Hard Disk (IDE) Connector

Pin

Signal

Pin

Signal

1

-RESET

2

GROUND

3

DATA 7

4

DATA 8

5

DATA 6

6

DATA 9

7

DATA 5

8

DATA 10

9

DATA 4

10

DATA 11

11

DATA 3

12

DATA 12

13

DATA 2

14

DATA 13

15

DATA 1

16

DATA 14

17

DATA 0

18

DATA 15

19

GROUND

20

NOT USED

21

Not Used

22

GROUND

23

-IOW A

24

GROUND

25

-IOR A

26

GROUND

27

-CHRDY A

28

DALE

29

Not Used

30

GROUND

31

-IRQ 14

32

-IO16

33

SA 1

34

NOT USED

35

SA 0

36

SA 2

37

CS 0

38

CS 1

39

HD LED A

40

GROUND

41

VCC

42

VCC

43

GROUND

44

Not Used

Table 3-2 CN3: Hard Disk (IDE) Connector