Pin description, Block diagram pin configuration – Cypress FS782 User Manual

Page 2

FS781/82/84

Document #: 38-07029 Rev. *F

Page 2 of 12

Output Frequency Selection

Loop Filter Selection Chart

The following table provides a list of recommended loop filter

values for the FS781/82/84. The FS78X is divided into four

ranges and operated at both 3.3V and 5.5 VDC. The loop filter

at the right is representative of the loop filter components in

Table 2.

Pin Description

Pin

Name

I/O

Type

Description

1/2 (SOIC)

3/4 (TSSOP)

X

IN

/X

OUT

I/O

Analog

Pins form an on-chip reference oscillator when connected to terminals

of an external parallel resonant crystal. X

IN

may be connected to

TTL/CMOS external clock source. If X

IN

is connected to an external clock

other than crystal, leave X

OUT

(pin 2) unconnected.

7/3 (SOIC)

1/5 (TSSOP)

S0 / S1

I

CMOS/TTL

Digital control inputs to select input frequency range and output

frequency scaling. Refer to Table 2 and Table 3 for selection. S0 has internal

pull-down. S1 has internal pull-up.

4 (SOIC)

6 (TSSOP)

LF

I

Analog

Loop Filter. Single ended three-state output of the phase detector. A two-pole

passive loop filter is connected to LF.

6 (SOIC)

8 (TSSOP)

FSOUT

O

CMOS/TTL

Modulated Clock Frequency Output. The center frequency is the same as

the input reference frequency for FS781. Input frequency is multiplied by 2×

and 4× for FS782 and FS784, respectively.

8 (SOIC)

2 (TSSOP)

V

DD

P

Power

Positive Power Supply.

5 (SOIC)

7 (TSSOP)

V

SS

P

Power

Power Supply Ground.

Table 1. FSOUT SSCG (Modulated Output Clock) Product Selection

Product Number

FSOUT Frequency Scaling

Description

FS781

1Ч

1Ч modulated frequency of input clock

FS782

2Ч

2Ч modulated frequency of input clock

FS784

4Ч

4Ч modulated frequency of input clock

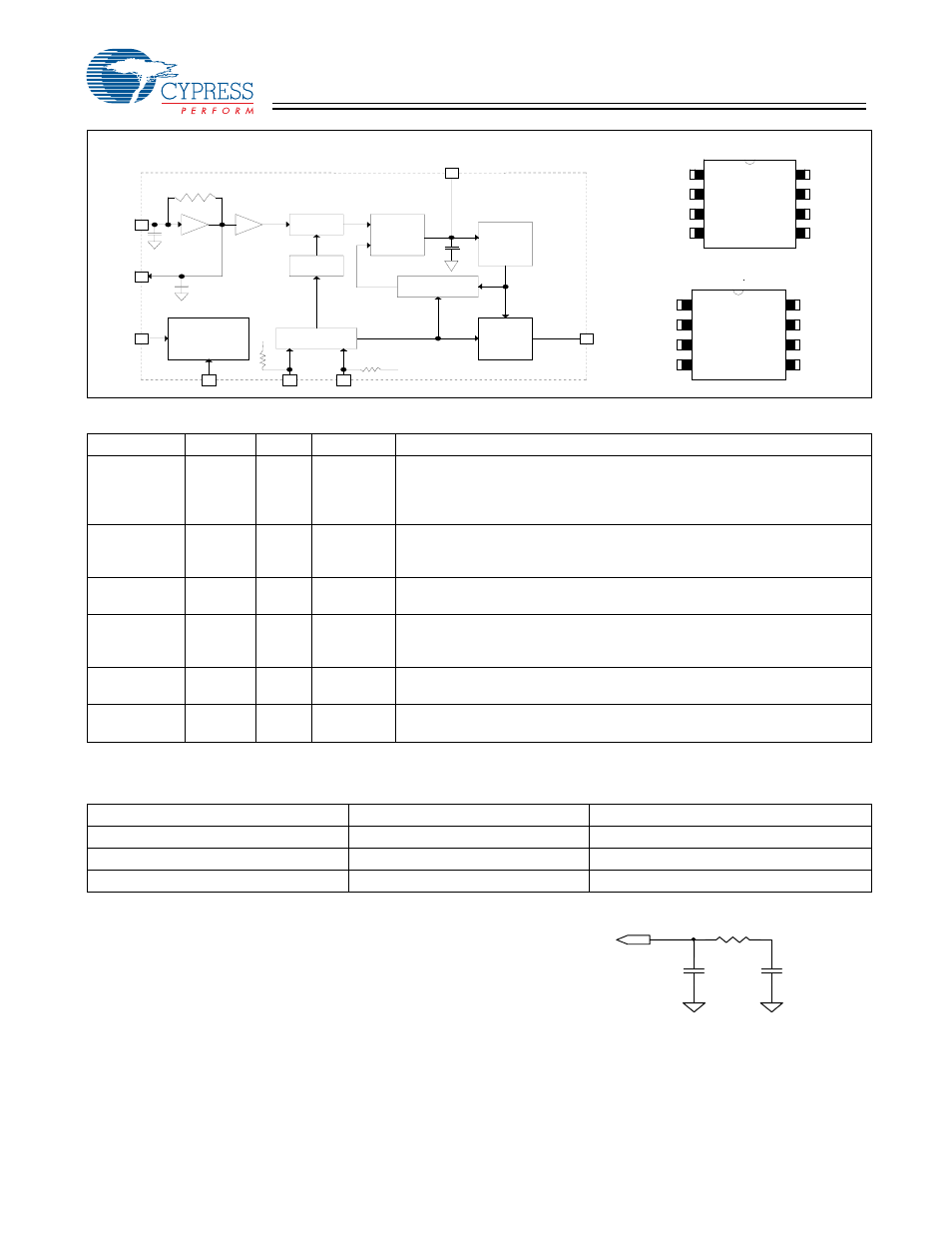

Block Diagram

Pin Configuration

Phase

Detector

VCO

1(3)

2(4)

Xin

Xout

10 pF.

Reference

Divider

8 pF

8 pF

250 K

VCO / N

Modulation

Control

Input Control Logic

Output

Divider

and

Mux

Power Contol

Logic

3(5)

7(1)

8(2)

5(7)

4(6)

VDD

S0

S1

FSOUT

Loop Filter

VSS

6(8)

VSS

VDD

(TSSOP Pin #)

1

2

3

4

8

7

6

5

Xin

Xout

S1

LF

VDD

S0

FSOUT

VSS

FS78x

8 Pin SOIC Package

1

2

3

4

8

7

6

5

S0

VDD

Xin

Xout

FSOUT

VSS

LF

S1

FS78x

8 Pin TSSOP Package

C8

R6

C7

LF (pin 4)