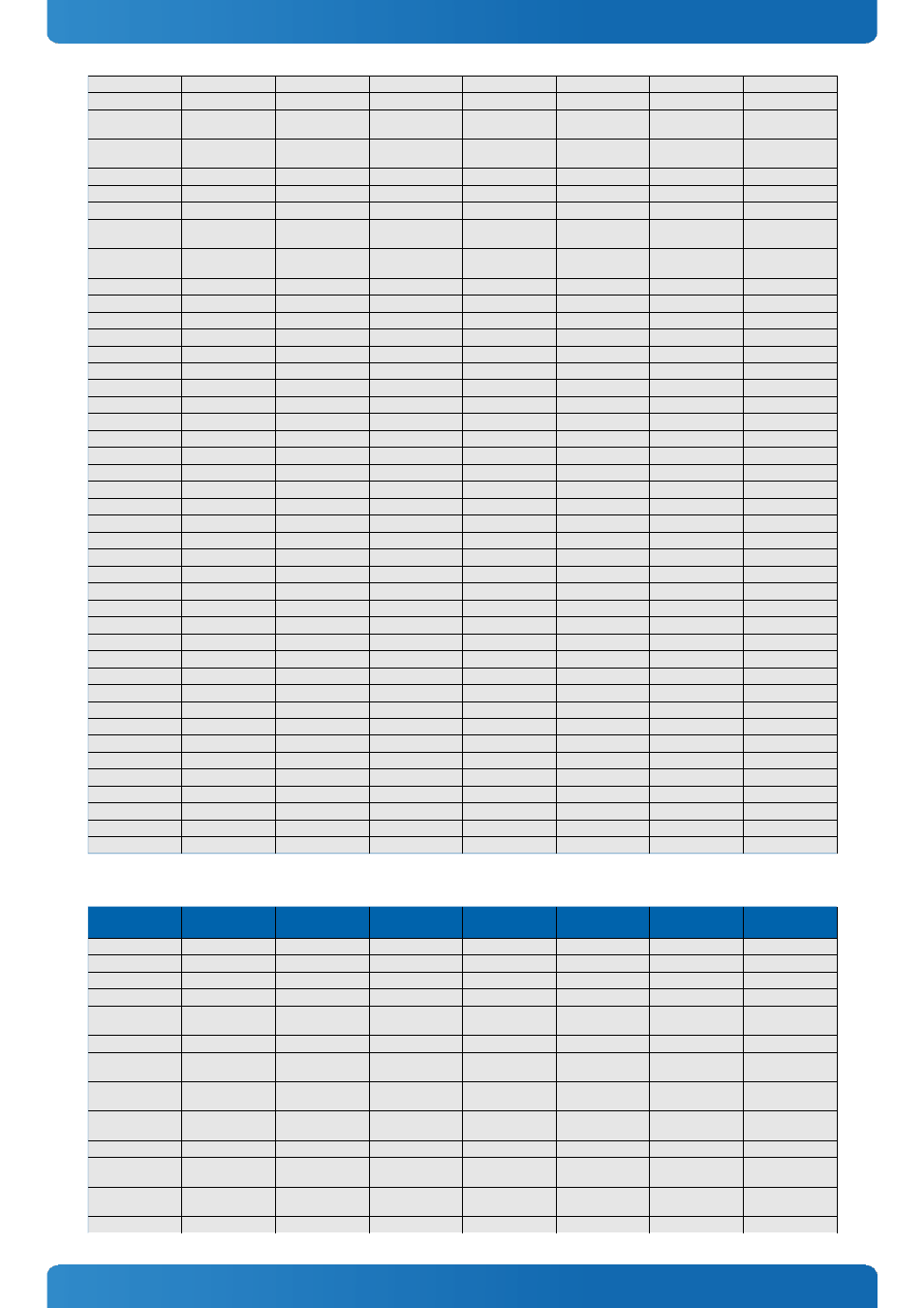

2 smarc™ connector bottom side, Smarc™ connector bottom side, Smarc-sxbti / connectors – Kontron SMARC-sXBTi User Manual

Page 30

SMARC-sXBTi / Connectors

P114

GPIO6 / TACHIN

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_92

V_1V8_S0

P115

GPIO7 / PCAM_FLD

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_97

V_1V8_S0

P116

GPIO8 / CAN0_ERR

#

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_98

V_1V8_S0

P117

GPIO9 / CAN1_ERR

#

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_99

V_1V8_S0

P118

GPIO10

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_100

V_1V8_S0

P119

GPIO11

Bi-Dir

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S0_SC_101

V_1V8_S0

P120

GND

-

-

-

-

-

-

P121

I2C_PM_CK

Out

PU-2k2

CMOS 1.8V

ValleyView

SIO_I2C_DATA_/_G

PIO_S0_SC_79

V_1V8_S0

P122

I2C_PM_DAT

Bi-Dir

PU-2k2

CMOS 1.8V

ValleyView

SIO_I2C_DATA_/_G

PIO_S0_SC_79

V_1V8_S0

P123

BOOT_SEL0#

In

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S5_0

V_1V8_S5

P124

BOOT_SEL1#

In

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S5_8

V_1V8_S5

P125

BOOT_SEL2#

In

PU-SoC-20k

CMOS / 1.8V

ValleyView

GPIO_S5_10

V_1V8_S5

P126

RESET_OUT#

Out

CPLD-Wpu

CMOS / 1.8V

CPLD

IO_B5

V_1V8_REG_S5

P127

RESET_IN#

In

PU-CPLD-20k

CMOS / 1.8V

CPLD

IO_J10

V_1V8_REG_S5

P128

POWER_BTN#

In

PU-CPLD-20k

CMOS / 1.8V

CPLD

IO_E10

V_1V8_REG_S5

P129

SER0_TX

Out

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART1_TXD

V_1V8_S0

P130

SER0_RX

In

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART1_RXD

V_1V8_S0

P131

SER0_RTS#

Out

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART1_RTS#

V_1V8_S0

P132

SER0_CTS#

In

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART1_CTS#

V_1V8_S0

P133

GND

-

-

-

-

-

-

P134

SER1_TX

Out

SoC 20k PU

CMOS / VDD_IO

ValleyView

GPIO_S0_SC_57

V_1V8_S0

P135

SER1_RX

In

SoC 20k PU

CMOS / VDD_IO

ValleyView

GPIO_S0_SC_61

V_1V8_S0

P136

SER2_TX

Out

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART2_TXD

V_1V8_S0

P137

SER2_RX

In

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART2_RXD

V_1V8_S0

P138

SER2_RTS#

Out

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART2_RTS#

V_1V8_S0

P139

SER2_CTS#

In

SoC 20k PU

CMOS / VDD_IO

ValleyView

SIO_UART2_CTS#

V_1V8_S0

P140

SER3_TX

NC

-

-

-

-

-

P141

SER3_RX

NC

-

-

-

-

-

P142

GND

-

-

-

-

-

-

P143

CAN0_TX

NC

-

-

-

-

-

P144

CAN0_RX

NC

-

-

-

-

-

P145

CAN1_TX

NC

-

-

-

-

-

P146

CAN1_RX

NC

-

-

-

-

-

P147

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P148

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P149

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P150

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P151

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P152

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P153

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P154

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P155

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

P156

VDD_IN

PWR

-

-

-

-

3.0V-5.25V

5.2

SMARC™ Connector Bottom Side

Pin

Signal

Module Direction

Module

Termination

Type/Tolerance

Controller

Controller Pin

Name

Power Rail

S1

PCAM_VSYNC

-

-

-

-

-

-

S2

PCAM_HSYNC

-

-

-

-

-

-

S3

GND

-

-

-

-

-

-

S4

PCAM_PXL_CK0

-

-

-

-

-

-

S5

I2C_CAM_CK

Out

PU-2k2

CMOS / 1.8V

ValleyView

SIO_I2C1_CLK_/_G

PIO_S0_SC_80

V_1V8_S0

S6

CAM_MCK

Out

-

CMOS / 1.8V

ValleyView

PMC_PLT_CLK0

V_1V8_S0

S7

I2C_CAM_DAT

Bi-Dir

PU-2k2

CMOS / 1.8V

ValleyView

SIO_I2C1_DATA_/_

GPIO_S0_SC_81

V_1V8_S0

S8

CSI0_CK+ /

PCAM_D10

In

-

LVDS D-PHY / 1.8V

ValleyView

MCSI3_CLKP

V_1V24_S0

S9

CSI0_CK- /

PCAM_D11

In

-

LVDS D-PHY / 1.8V

ValleyView

MCSI3_CLKN

V_1V24_S0

S10

GND

-

-

-

-

-

-

S11

CSI0_D0+ /

PCAM_D12

In

-

LVDS D-PHY / 1.8V

ValleyView

MCSI1_DP2

V_1V24_S0

S12

CSI0_D0- /

PCAM_D13

In

-

LVDS D-PHY / 1.8V

ValleyView

MCSI1_DN2

V_1V24_S0

S13

GND

-

-

-

-

-

-

30