3 lpc, Come-bhl6 / features and interfaces – Kontron COMe-bHL6 User Manual

Page 38

COMe-bHL6 / Features and Interfaces

4.3

LPC

The Low Pin Count (LPC) Interface signals are connected to the LPC Bus bridge located in the CPU or chipset. The LPC low

speed interface can be used for peripheral circuits such as an external Super I/O Controller, which typically combines

legacy-device support into a single IC. The implementation of this subsystem complies with the COM Express®

Specification. Implementation information is provided in the COM Express® Design Guide maintained by PICMG. Please

refer to the official PICMG documentation for additional information.

The LPC bus does not support DMA (Direct Memory Access) and a clock buffer is required when more than one device is

used on LPC. This leads to limitations for ISA bus and SIO (standard I/O´s like Floppy or LPT interfaces) implementations.

All Kontron COM Express® Computer-on-Modules imply BIOS support for following external baseboard LPC Super I/O

controller features for the

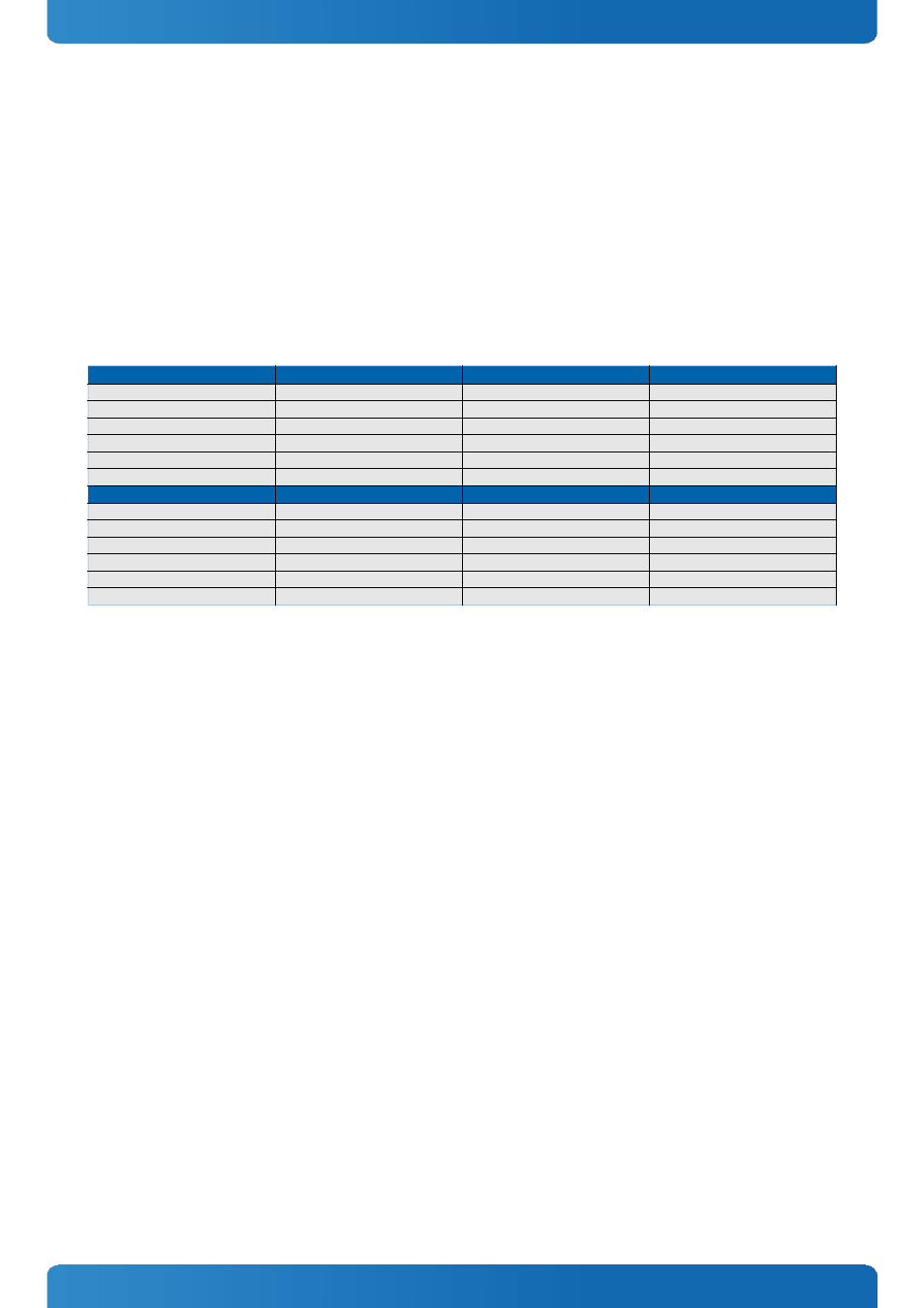

Winbond/Nuvoton 5V 83627HF/G and 3.3V 83627DHG-P:

83627HF/G

Phoenix BIOS

AMI CORE8

AMI / Phoenix EFI

PS/2

YES

YES

YES

COM1/COM2

YES

YES

YES

LPT

YES

YES

YES

HWM

YES

YES

NO

Floppy

NO

NO

NO

GPIO

NO

NO

NO

83627DHG-P

Phoenix BIOS

AMI CORE8

AMI / Phoenix EFI

PS/2

YES

YES

YES

COM1/COM2

YES

YES

YES

LPT

YES

YES

YES

HWM

NO

NO

NO

Floppy

NO

NO

NO

GPIO

NO

NO

NO

Features marked as not supported do not exclude OS support (e.g. HWM can be accessed via SMB). For any other LPC

Super I/O additional BIOS implementations are necessary. Please contact your local sales or support for further details.

38