Dell PowerEdge R820 User Manual

Page 7

7

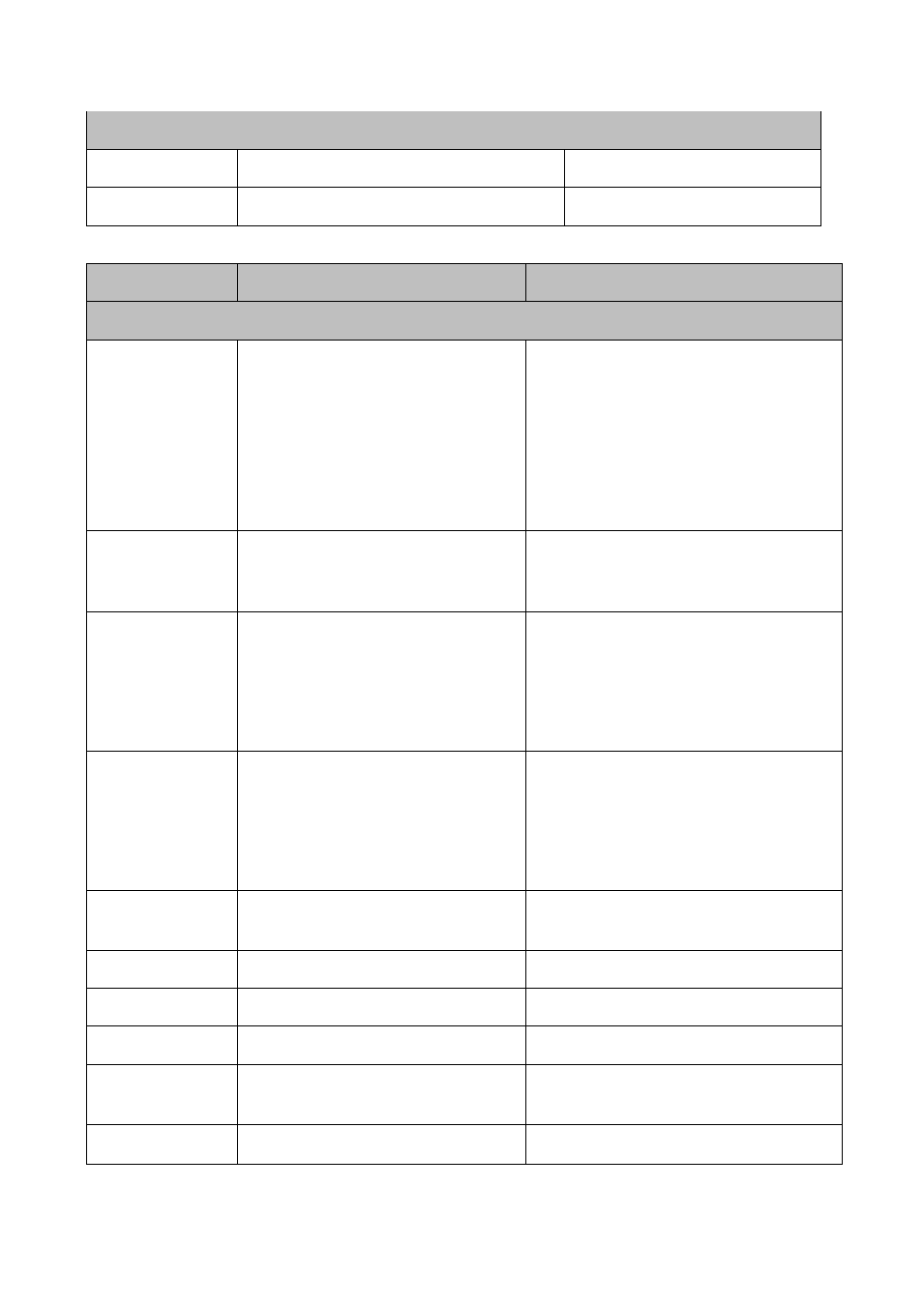

IDSDM

SPI Flash

Exclusively used by the controller

SPI interface via iDRAC

MCU

Firmware

USB interface via PCH

Item

How is this memory write protected?

How is the memory cleared?

Planer

PCH Internal CMOS

RAM

N/A – BIOS only control

1) Set NVRAM_CLR jumper to clear BIOS

configuration settings at boot and reboot

system;

2) AC power off system, remove coin cell

battery for 30 seconds, replace battery and

power back on;

3) restore default configuration in F2 system

setup menu.

BIOS SPI Flash

Software write protected

Not possible with any utilities or applications

and system is not functional if

corrupted/removed.

iDRAC SPI Flash

Embedded iDRAC subsystem firmware

actively controls sub area based write

protection as needed.

Not completely user clearable; however, user

data, lifecycle log and archive, SEL, fw image

repository can be cleared via Delete

Configuration and Retire System, accessible in

Lifecycle Controller interface

BMC EMMC

Embedded FW write protected

Not completely user clearable; however, user

data, lifecycle log and archive, SEL, fw image

repository can be cleared via Delete

Configuration and Retire System, accessible in

Lifecycle Controller interface

CPU Vcore and VSA

Regulators

There are passwords for different sections

of the register space

Not user clearable

System CPLD RAM

Not accessible

Not accessible

System Memory

OS Control

Reboot or power down system

Internal USB Key

No write protect

Can be cleared in system OS

Trusted Platform

Module (TPM)

SW write protected

F2 Setup option

PEM FRU

Hardware strapping

Not user clearable