Cypress CY25822-2 User Manual

Page 4

CY25822-2

Document #: 38-07531 Rev. **

Page 4 of 9

Bytes 2 through 5: Reserved Registers

PWRDWN# (Power-down) Clarification

The PWRDWN# (Power-down) pin is used to shut off ALL

clocks prior to shutting off power to the device. PWRDWN# is

an asynchronous active LOW input. This signal is synchro-

nized internally to the device powering down the clock synthe-

sizer. PWRDWN# is an asynchronous function for powering up

the system. When PWRDWN# is low, all clocks are driven to

a LOW value and held there and the VCO and PLLs are also

powered down. All clocks are shut down in a synchronous

manner so has not to cause glitches while transitioning to the

low ‘stopped’ state. When PWRDWN# is deasserted the

clocks should remain stopped until the VCO is stable and

within specification (t

STABLE

). A stopped clock is either

tri-stated or driven low depending on the state of the tri-state

enable I

2

C register bit. CY25822 clocks that are stopped in the

driven state are driven low.

The CLKIN input must be on and within specified operating

parameters before PWRDWN# is asserted and it must remain

in this state while PWRDWN# is asserted.

0

1

0

1

Down

2.0

0

1

1

0

Down

2.5

0

1

1

1

Down

3.0

1

0

0

0

Center

±0.3

1

0

0

1

Center

±0.4

1

0

1

0

Center

±0.5

1

0

1

1

Center

±0.6

1

1

0

0

Center

±0.8

1

1

0

1

Center

±1.0

1

1

1

0

Center

±1.25

1

1

1

1

Center

±1.5

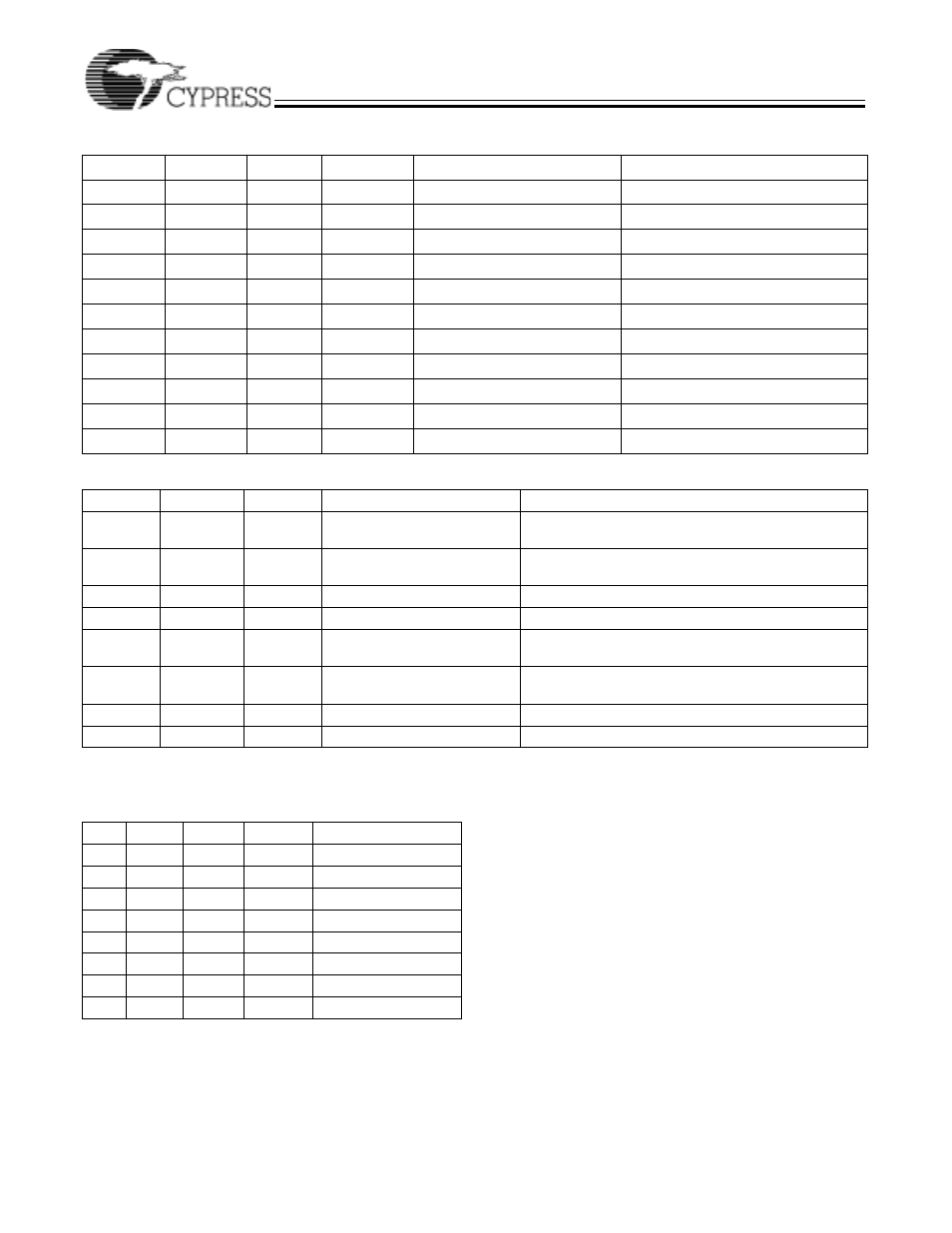

Table 4. Spread Spectrum Select (continued)

SS3

SS2

SS1

SS0

Spread Mode

Spread Amount%

Byte 1: Control Register

Bit

@Pup

Pin#

Name

Pin Description

7

1

5

REFEN

REFOUT enable

0 = disabled, 1 = enabled

6

1

5

REFSLEW

REFOUT edge rate control

0 = slow, 1 = nominal

5

0

Not Applicable

Reserved.

4

0

Not Applicable

Reserved

3

1

4

CLKSLEW

CLKOUT edge rate control

0 = slow, 1 = nominal

2

1

4

CLKEN

CLKOUT enable

0 =disabled, 1 = enabled

1

0

Not Applicable

Reserved

0

0

Not Applicable

Reserved

Byte 6: Vendor/Revision ID Register

Bit

@Pup

Pin#

Name

Pin Description

7

0

–

–

Revision ID Bit 3

6

0

–

–

Revision ID Bit 2

5

0

–

–

Revision ID Bit 1

4

0

–

–

Revision ID Bit 0

3

1

–

–

Vendor ID Bit 3

2

0

–

–

Vendor ID Bit 2

1

0

–

–

Vendor ID Bit 1

0

0

–

–

Vendor ID Bit 0