Cypress CY25822-2 User Manual

Page 2

CY25822-2

Document #: 38-07531 Rev. **

Page 2 of 9

Serial Data Interface

To enhance the flexibility and function of the clock synthesizer,

a two-signal serial interface is provided. Through the Serial

Data Interface, various device functions such as individual

clock output buffers, etc., can be individually enabled or

disabled.

The registers associated with the Serial Data Interface

initializes to their default setting upon power-up, and therefore

use of this interface is optional. Clock device register changes

are normally made upon system initialization, if any are

required. The interface can also be used during system

operation for power management functions.

Data Protocol

The clock driver serial protocol accepts byte write, byte read,

block write, and block read operation from the controller. For

block write/read operation, the bytes must be accessed in

sequential order from lowest to highest byte (most significant

bit first) with the ability to stop after any complete byte has

been transferred. For byte write and byte read operations, the

system controller can access individual indexed bytes. The

offset of the indexed byte is encoded in the command code, as

described in Table 1.

The block write and block read protocol is outlined in Table 2

while Table 3 outlines the corresponding byte write and byte

read protocol.The slave receiver address is 11010100 (D4h).

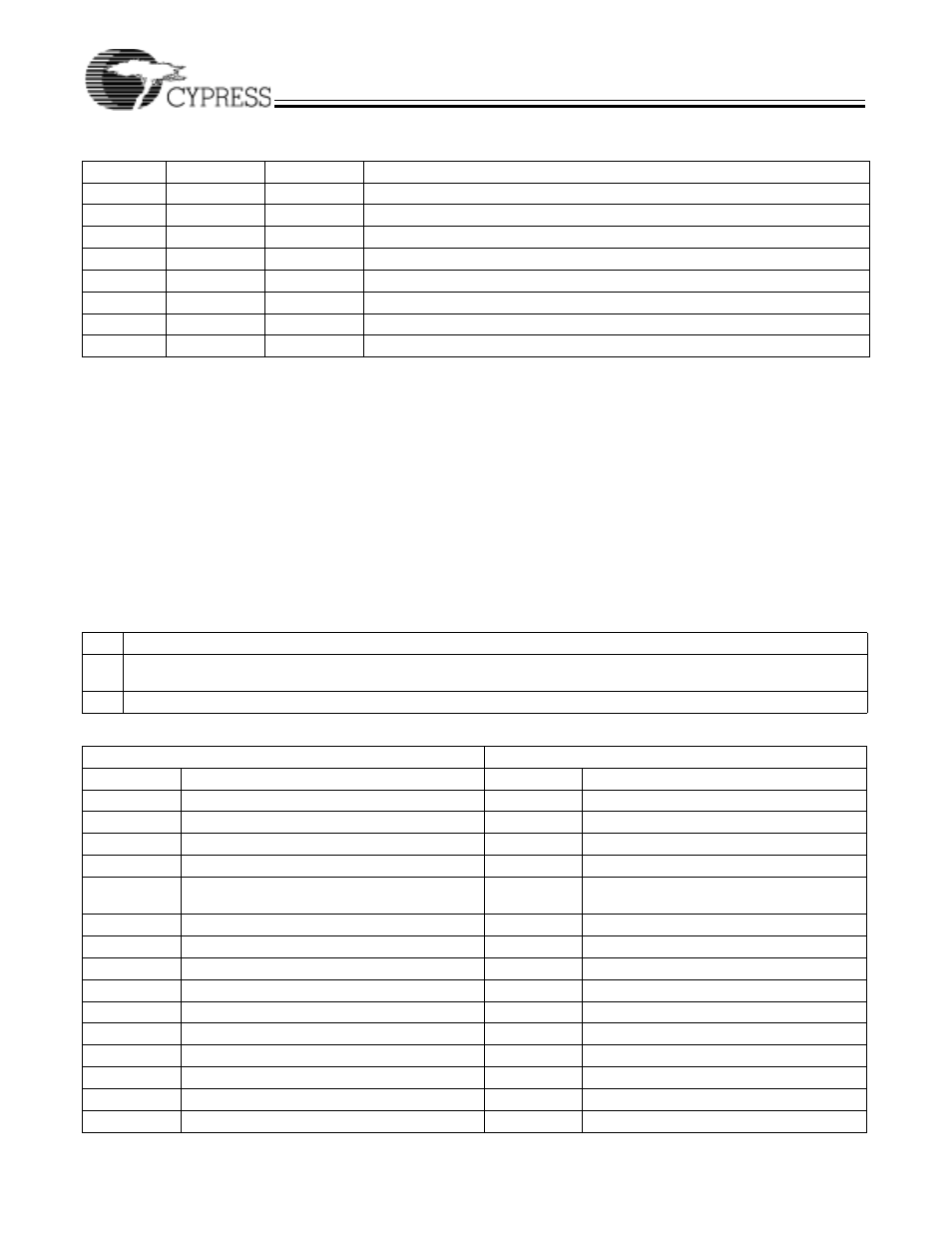

Pin Description

Pin No.

Pin Name

Pin Type

Pin Description

1

CLKIN

Input

48-MHz or 66-MHz Clock Input.

2

VDD

Power

Power Supply for PLL and Outputs.

3

GND

Ground

Ground for Outputs.

4

CLKOUT

Output

48-MHz or 66-MHz Spread Spectrum Clock Output.

5

REFOUT

Output

Non-spread Spectrum Reference Clock Output.

6

SDATA

I/O

I

2

C-compatible SDATA.

7

SCLOCK

Input

I

2

C-compatible SCLOCK.

8

PWRDWN#

Output

LVTTL Input for PowerDown# Active Low.

Table 1. Command Code Definition

Bit

Description

7

0 = Block read or block write operation

1 = Byte read or byte write operation

(6:0) Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be ’0000000’

Table 2. Block Read and Block Write Protocol

Block Write Protocol

Block Read Protocol

Bit

Description

Bit

Description

1

Start

1

Start

2:8

Slave address – 7 bits

2:8

Slave address – 7 bits

9

Write = 0

9

Write = 0

10

Acknowledge from slave

10

Acknowledge from slave

11:18

Command Code – 8 bits

'00000000' stands for block operation

11:18

Command Code – 8 bits

'00000000' stands for block operation

19

Acknowledge from slave

19

Acknowledge from slave

20:27

Byte Count – 8 bits

20

Repeat start

28

Acknowledge from slave

21:27

Slave address – 7 bits

29:36

Data byte 1 – 8 bits

28

Read = 1

37

Acknowledge from slave

29

Acknowledge from slave

38:45

Data byte 2 – 8 bits

30:37

Byte count from slave – 8 bits

46

Acknowledge from slave

38

Acknowledge

....

......................

39:46

Data byte from slave – 8 bits

....

Data Byte (N–1) –8 bits

47

Acknowledge

....

Acknowledge from slave

48:55

Data byte from slave – 8 bits