5 status bits, Status bits, Process data transfer – Lenze E82ZAFPC010 User Manual

Page 55

Process data transfer

DRIVECOM control

Status bits

l

55

EDS82ZAFPC010 EN 4.0

7.2.5

Status bits

Status bits

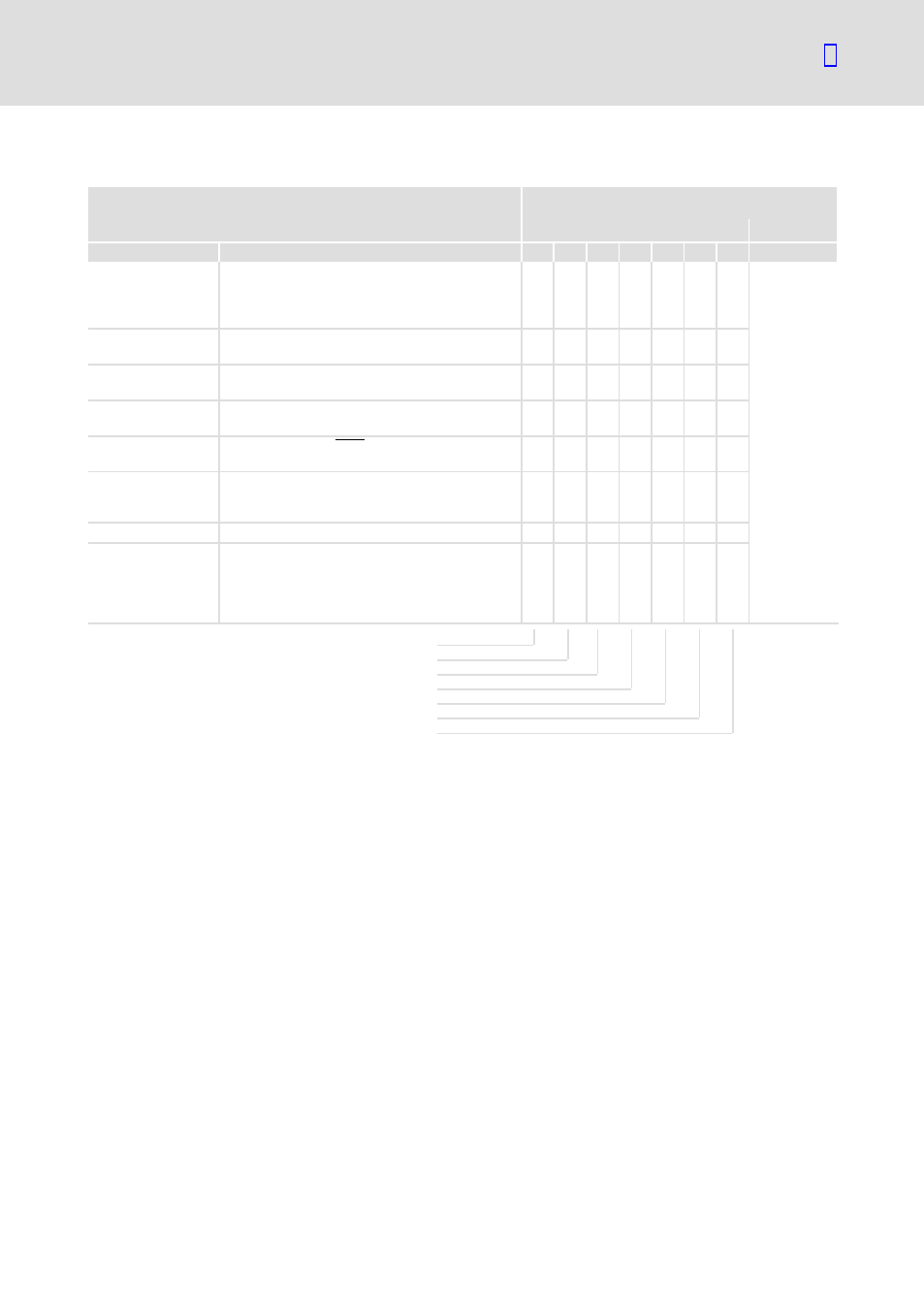

The current device status is unambiguously coded in the bits 0 ... 6 of

the status word:

Bits of the status word

Note

Device status

Meaning

6

5

4

3

2

1

0

Not ready to switch

on

Controller is being initialised and is not yet ready

to operate.

After initialisation automatically

ð "Ready to

switch on"

0

x

x

0

0

0

0

1 Bit set

Switch−on inhibit

Controller inhibited (CINH).

Waiting for "Standstill" command

1

x

x

0

0

0

0

Ready to switch on

Controller inhibited (CINH).

Waiting for "Switch−on" command

0

1

x

0

0

0

1

0 Bit not

set

Switched on

Controller inhibited (CINH).

Waiting for "Operation enabled" command.

0

1

x

0

0

1

1

Operation enabled

Controller enabled (CINH).

Pulse inhibit can be set automatically

0

1

x

0

1

1

1

x Any bit

status

Fault reaction active

Fault (TRIP) recognised, a time−based,

fault−dependent reaction is executed.

Then automatically

ð "Fault"

0

x

x

1

1

1

1

Fault

Controller is in the device status "Fault".

0

x

x

1

0

0

0

Quick stop (QSP)

active

"Quick stop (QSP)" command has been sent in the

device status "Operation enabled"

ð controlled

deceleration via the quick stop ramp.

After deceleration automatically

ð "Switch−on

inhibit"

0

0

x

0

1

1

1

Switch−on inhibit

Quick stop (QSP)

Inhibit voltage

Fault

Operation enabled

Switched on

Ready to switch on