Cobranet™ ev-2 – Cirrus Logic EV2 User Manual

Page 19

CobraNet™ EV-2

19

Rev. 2.1

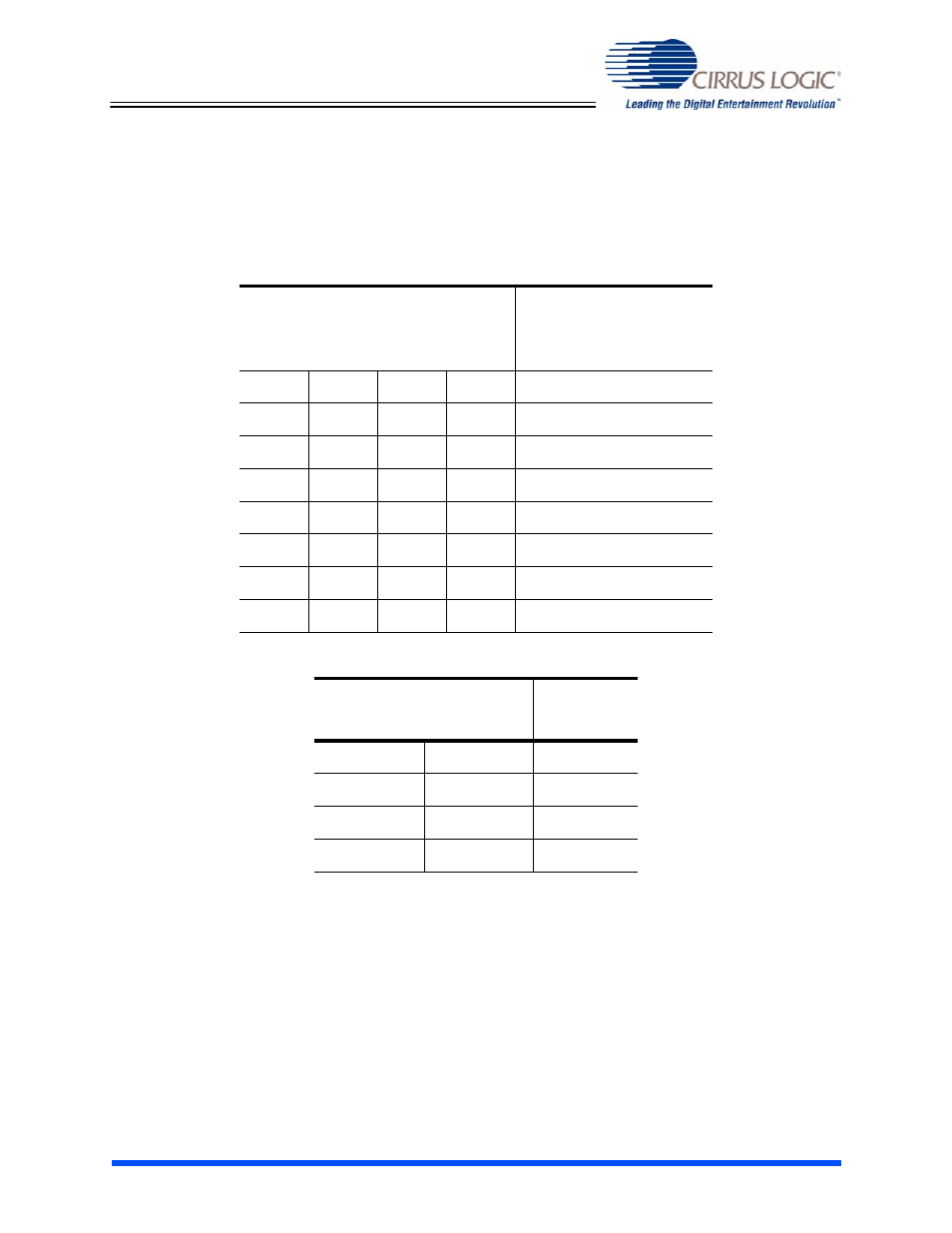

Sine Wave Generator

The FPGA contains a 32-sample, 24-bit, sine table. The table is stepped through at the

sample clock rate so the resulting fundamental frequency is 48kHz / 32 samples =

1500Hz and 3000Hz at 96kHz. Limited control over frequency and gain is provided.

Listed below are the values to write to the frequency and gain registers in the FPGA.

Frequency register data bits

AD3 AD2 AD1 AD0

Frequency

48kHz sample rate

(96kHz sample rate)

0

0

0

1

1.5 kHz (3.0 kHz)

0

0

1

0

3.0 kHz (6.0 kHz)

0

0

1

1

4.5 kHz (9.0 kHz)

0

1

0

0

6.0 kHz (12.0 kHz)

0

1

0

1

7.5 kHz (15.0 kHz)

0

1

1

0

9.0 kHz (18.0 kHz)

0

1

1

1

10.5 kHz (21.0 kHz)

1

0

0

0

12.0 kHz (24.0 kHz)

Table 8: Sine Wave Frequency Register Bit Definitions

Gain register data bits

AD1 AD0

Gain

0

0

0dB

0

1

-6dB

1

0

-12dB

1

1

-18dB

Table 9: Sine Wave Gain Register Bit Definitions

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)