Boot mode pin latching, An273 – Cirrus Logic AN273 User Manual

Page 3

AN273

3

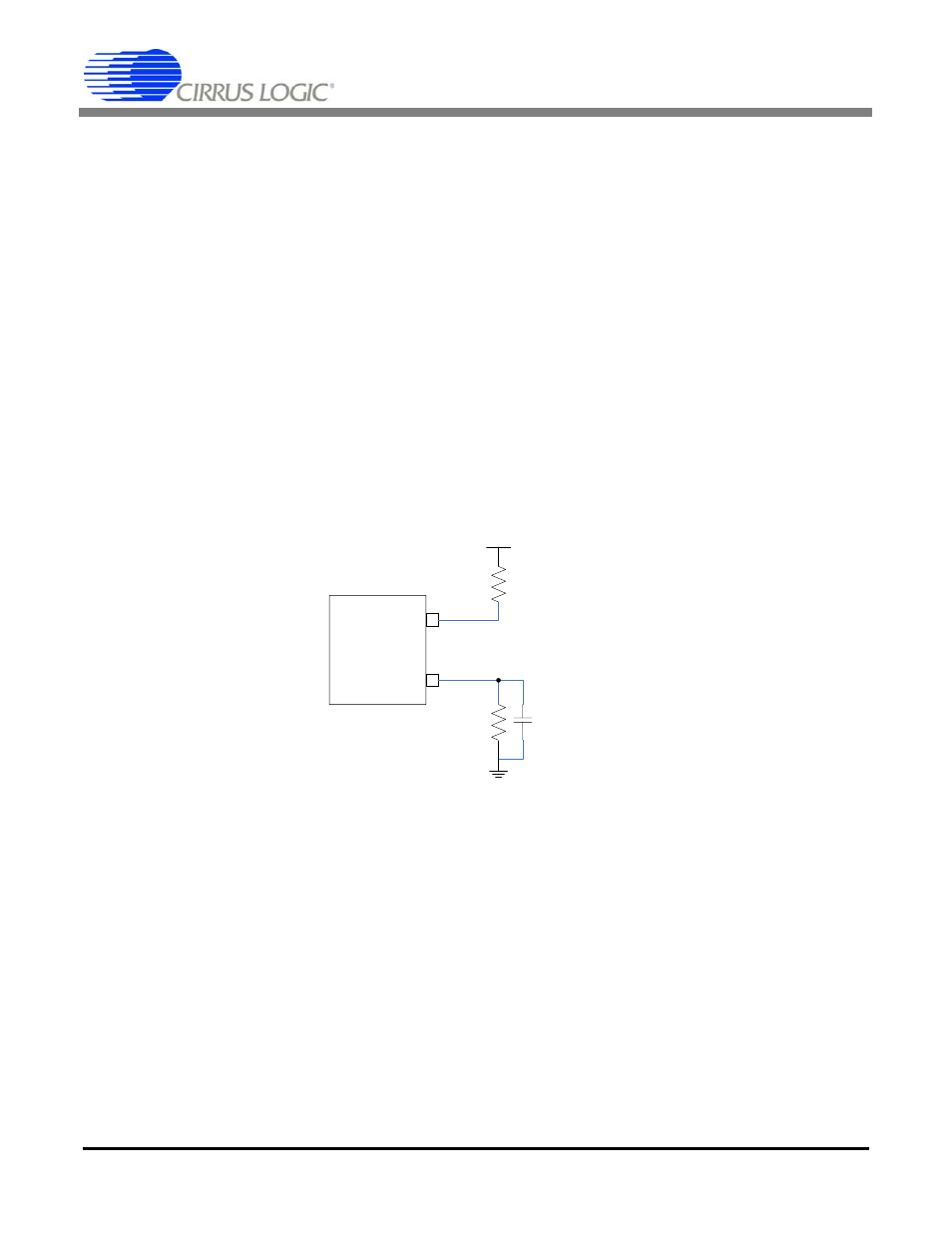

7. Boot Mode Pin Latching

An issue exists where boot mode pins may not properly latch a logic zero when RSTOn de-asserts. Boot

mode pins that may exhibit this issue are: CSn7, CSn6, CSn2 and CSn1. The other boot mode pins are

not affected.

Boot mode pins are latched on the rising edge of RSTOn. This pin is open collector and may have slow

rise times, depending on the value of the external pull up resistor connected to this pin. The boot mode

pins require a 5ns minimum hold time after RSTOn is de-asserted. If the timing is not met, boot mode pins

intended to be latched as a logic zero may be latched as a logic one.

To prevent this issue, the following is recommended:

-

To reduce rise time to approximately 200 ns maximum, place a 1k pull up resistor on RSTOn.

-

Place a small capacitor on the required boot mode signal to delay the signal from rising too quickly after

RSTOn is released. The value of the capacitor is dependant on the system design. A capacitor in the range

of 100-220pF is recommended. This is only required for pins that need to be latched as a logic zero. Refer

to the following diagram.

RSTOn

CSnX

1K

2.2K

3.3V

100-220pF

EP93xx