Cirrus Logic AN181 User Manual

Using the crystal

1

Copyright

Cirrus Logic, Inc. 2000

(All Rights Reserved)

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

AN181

Application Note

USING THE CRYSTAL

®

CS8900A IN 8-BIT MODE

By James Ayres

Introduction

The CS8900A is a good candidate for designs with

an 8-bit data bus. Because of its small size and

built-in filters the chip will take up a minimum of

board space while providing a cost effective, high

performance Ethernet connection. This application

note shows how to use the CS8900A in 8 bit mode,

including software information for the programmer

and a typical connection diagram for the design en-

gineer.

References

The designer should familiarize himself with the

Connecting to non-ISA bus systems chapter in the

CS8900A Technical Reference Manual, Low cost,

high performance Ethernet Controller for non-

ISA systems. This chapter is a reference on how to

easily connect the chip to a non-ISA processor. It

includes diagrams connecting the CS8900A to a

MC68302, a Cirrus Logic CL-PS7111, and a Hita-

chi SH3. That chapter contains most of the data

needed for the design engineer. The data sheet is

the source for functional descriptions of the regis-

ters, receive operation, transmit operation, timing

etc. Only the 8-bit specific issues will be covered

in this application note.

Software Drivers

There are many software drivers available for the

CS8900A in 16-bit mode, including VxWorks™,

Psos

®

, Linux

®

, Packet Driver and ATI Nucleus.

Source code for the VxWorks, Linux, and Psos are

available on the Cirrus Website. The Linux driver,

in particular, is a good starting point for writing a

custom driver in C. Porting any driver for 8-bit op-

eration is the customer’s responsibility.

I/O Ports

In 8 bit mode the CS8900A is accessed through its

eight 16 bit I/O ports.

In a non-ISA system these ports are usually memo-

ry mapped into standard system memory. Please

note that the driver should read or write both bytes

when accessing any CS8900A status or event reg-

ister.

Frame Transmission

Transmission and reception of frames is done

through these data ports. The basic steps in trans-

mitting a frame are 1) bid for buffer space on the

chip by writing the transmit command to the TxC-

MD port and the length to TxLength port then

checking the BusSt register. 2) if space is available

begin writing the data, a byte at a time, to Re-

ceive/Transmit data port 0. Refer to the section I/O

Space Operation of the data sheet for more details.

For instance, the CS8900A is at its default I/O lo-

cation of 300h. To transmit a frame that is 81 bytes

in length the driver would first write the transmit

command 00C0h (Start transmitting after all bytes

transferred) to the TxCMD port. This is done by

writing the low order byte, C0h, to 304h then writ-

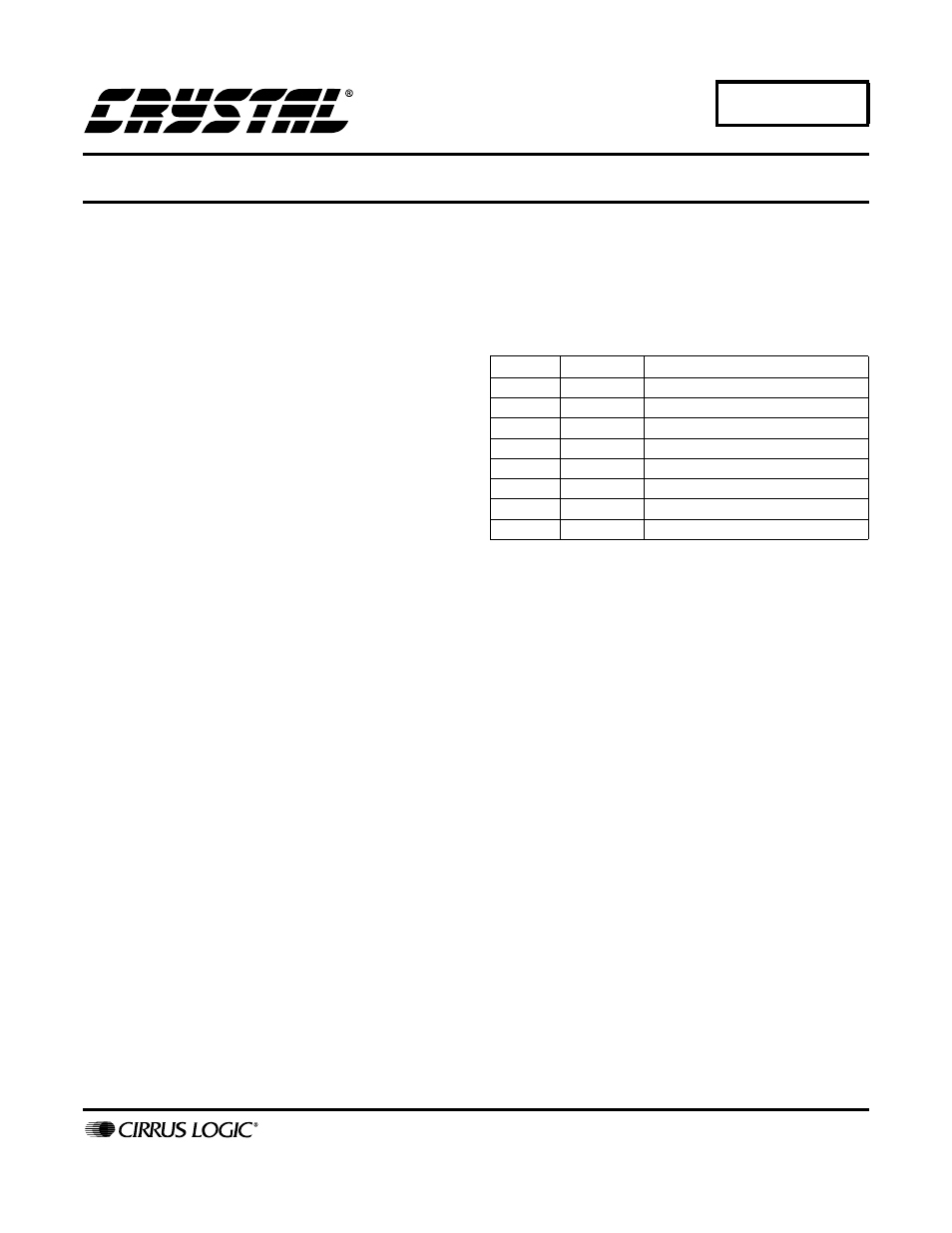

Offset

Type

Description

0000h

Read/Write Receive/Transmit Data (Port 0)

0002h

Read/Write Receive/Transmit Data (Port 1)

0004h

Write-only

TxCMD (Transmit Command)

0006h

Write-only

TxLength (Transmit Length)

0008h

Read-only

Interrupt Status Queue

000Ah

Read/Write

PacketPage Pointer

000Ch

Read/Write

PacketPage Data (Port 0)

000Eh

Read/Write

PacketPage Data (Port 1)

Table 1. I/O Mode Mapping

JAN ‘00

AN181REV1