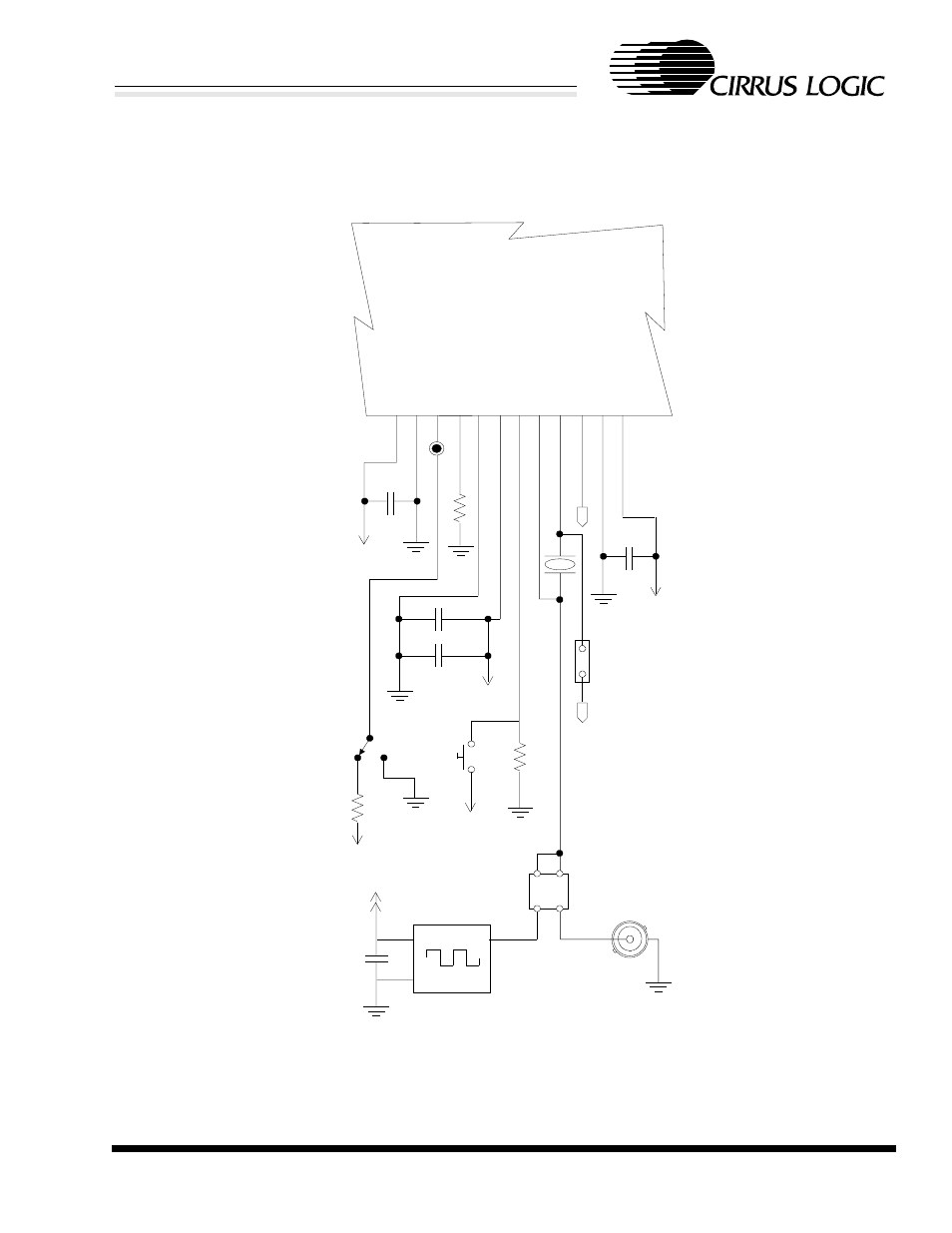

Figure 4. timing circuitry, Dual line interface unit – Cirrus Logic CDB61584A User Manual

Page 9

DS261DB2

59

CDB61584A

Dual Line Interface Unit

RV

+

1

RG

ND1

MOD

E

BG

R

E

F

AG

N

D

AV

+

RE

S

E

T

RE

F

C

L

K

XT

AL

O

U

T

1X

CLK

RG

N

D

2

RV

+

2

U7

CS61584A

TIMING CIRCUITRY

29

40

C5

.1

µ

F

VD+

R23

47K

R10

4.

99k

C6

C7

.1

µ

F

1.0

µ

F

VD+

VD+

VD+

SW1

1

2

R11

10K

Y1

1X

CLK

4

2

1

3

J14

8

VCC

GND

C14

.1

µ

F

U4

REFCLK

J15

C8

.1

µ

F

VD+

J 10

(must not

be jumped)

VA+

30

31

32

33

34

35

36

37

38

39

SW6

Figure 4. Timing Circuitry

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)