Cirrus Logic AN270 User Manual

An270, Introduction

Copyright

© Cirrus Logic, Inc. 2005

(All Rights Reserved)

Audio A/D Conversion

with an Asynchronous Decimation Filter

1. INTRODUCTION

Modern high-performance delta-sigma analog-to-digital (A/D) and digital-to-analog (D/A) audio conversion systems

require a high frequency system clock (master clock) for their conversion processes, generally in excess of 12 MHz.

Jitter on this clock is a significant source of performance degradation in these systems. This is generally not a prob-

lem in products that include the converters as well as a crystal based clock. However, this can be a particularly dif-

ficult problem to address in networked audio systems, recording systems which utilize a “house sync” signal and

other systems that require long-distance routing of the high frequency clocking signal within the system, such as a

mixing console. A common denominator of these systems is that the conversion nodes and the network operate at

the same sample rate or within the same clock domain. The most common approach to recover a low-jitter master

clock in these systems is to make use of a phase-lock-loop (PLL). PLL circuits take several forms and have their

advantages. However, often times the jitter performance is less than desirable or the PLL does not have a sufficient

frequency range, especially in voltage controlled crystal oscillator circuits, to cover all of the required sample rates.

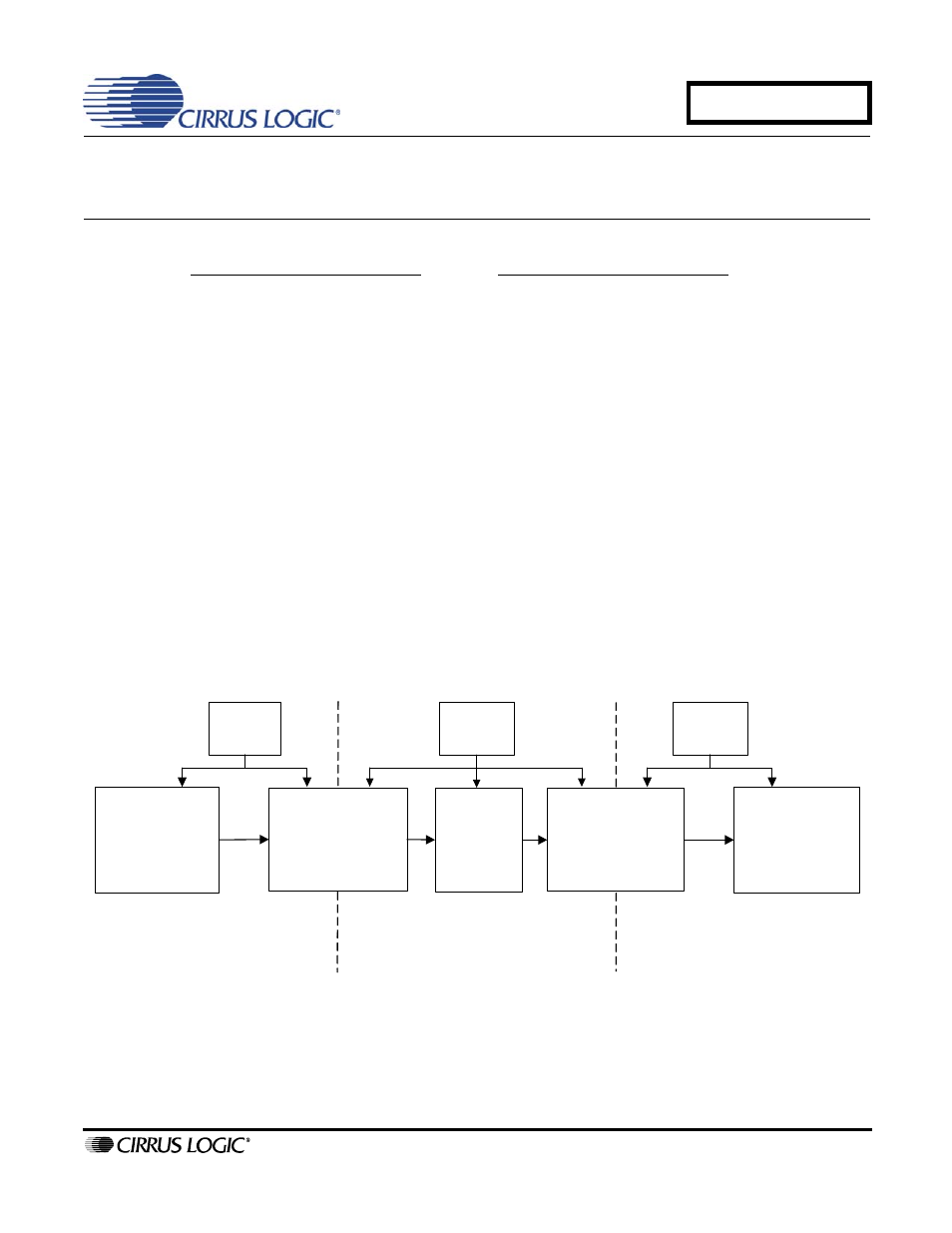

An alternative approach is to create a system architecture where the A/D and D/A conversion nodes operate within

local clock domains which are independent of the network or system clock domain. A system with independent clock

domains can easily be accomplished with the use of a sample rate converter (SRC), as shown in Figure 1. This ar-

chitecture also allows the conversion processes to operate at a fixed sample rate which is always higher than the

network or interface sample rate. The fundamental advantage of this approach is that the conversion processes are

immune to interface clock jitter and are controlled by a local jitter-free crystal oscillator.

Figure 1. Audio System Architecture with Independent Clock Domains

Crystal

Oscillator

CS5381

A/D

A/D Sampling

Clock Domain

Interface

Clock Domain

CS8421Asynchronous

Sample Rate Converter

CS4398

D/A

D/A Conversion

Clock Domain

Crystal

Oscillator

CS8421Asynchronous

Sample Rate Converter

DSP

System

Word Clock

AN270

MAY '05

AN270REV1

Steve Green

Technical Marketing Manager

Thomas Hoff

Applications Engineer