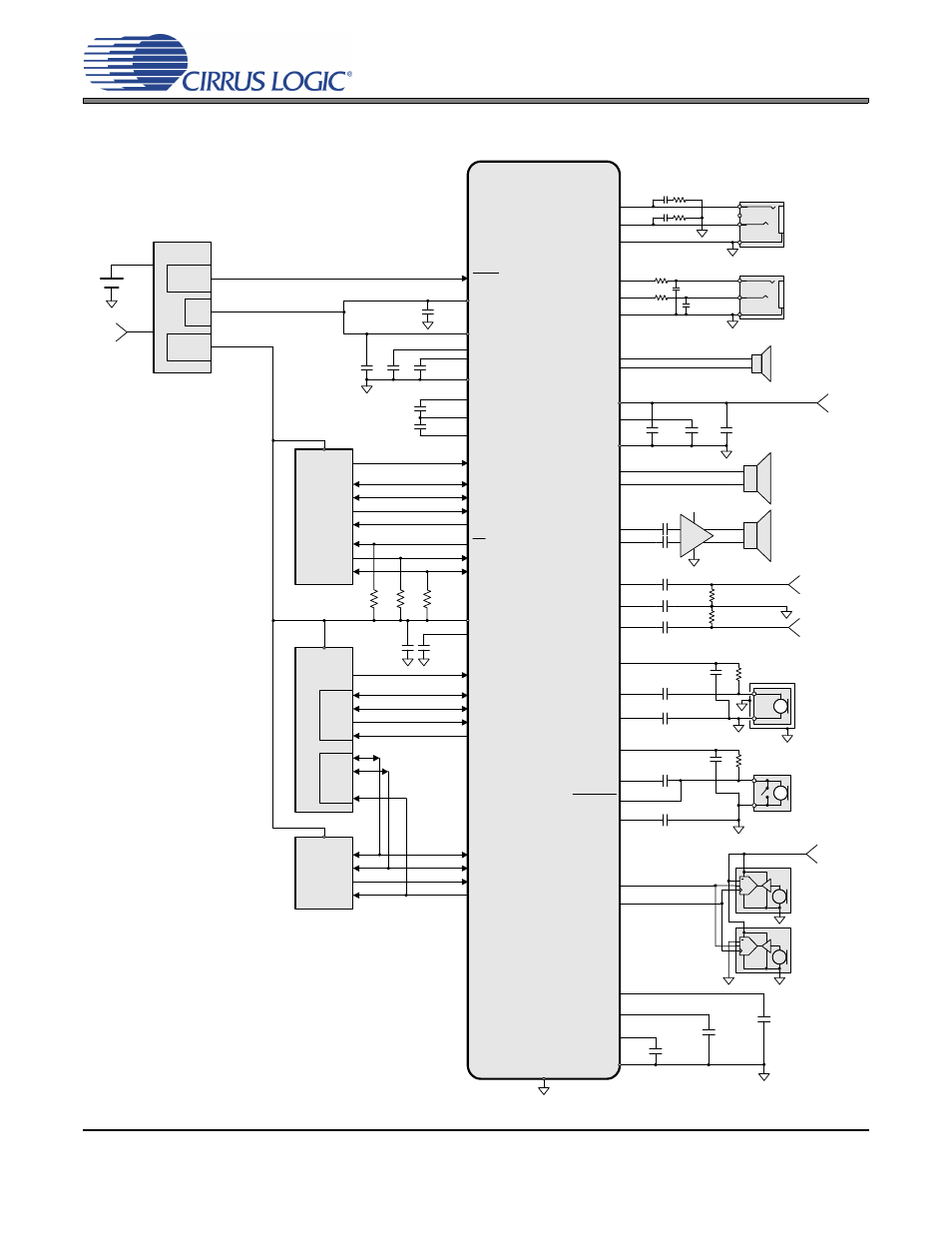

Typical connection diagram, Cs42l73 – Cirrus Logic CS42L73 User Manual

Page 4

4

CS42L73

1. TYPICAL CONNECTION DIAGRAM

Optional

Bias Res.

DGND

VL

SCL

SDA

R

P

ASP_LRCK

Applications

Processor

ASP_SCLK

ASP_SDIN

ASP_SDOUT

CS42L73

MIC2_BIAS

Line Level Out

Left & Right

SPKOUT+

SPKOUT-

MIC2

MIC2_REF

2.2 µF

SPK_VQ

AGND

2.2 µF

FILT+

EAROUT+

EAROUT-

VP

VBAT

LINEINA

Line In

Left

100 k

Ω

LINEINB

Line In

Right

100 k

Ω

0.1 µF

4.7 µF

2.2 µF

+VCP_FILT

FLYC

FLYN

-VCP_FILT

2.2 µF

2.2 µF

VCP

VANA

FLYP

2.2 µF

HPOUTB

HPOUTA

100

Ω

33 nF

HPOUT_REF

LINEOUTB

LINEOUTA

LINEIN_REF

VSP_LRCK

Baseband

Processor

MCLK1

VSP_SCLK

VSP_SDIN

VSP_SDOUT

2.2 µF

VD_FILT

1 µF

LINEO_REF

CPGND

PGND

MIC1_BIAS

MIC1

MIC1_REF

R

P

ANA_VQ

4.7 µF

INT

RESET

1 µF

Headphone Out

Left & Right

100

Ω

33 nF

Speakerphone

(Left)

Ear Speaker

(Receiver)

+

+

+

+

+

R

I_P

2200 pF

C0G

390

Ω

390

Ω

2200 pF

C0G

Optional

LPF

Ground Ring

0.1 µF

MCLK2

DMIC_SD

DMIC_SCLK

SPKLINEO+

SPKLINEO-

XSP_LRCK

XSP_SCLK

XSP_SDIN

XSP_SDOUT

MICB_FILT

4.7 µF

+

R

BIAS

Headset

Microphone

Handset

Microphone

1 µF

R

BIAS

MIC2_SDET

Speakerphone

(Right)

L/R

DATA

L/R

DATA

Bluetooth®

Transceiver

Cellular

Voice

SP

AEC

SP

Right/Data2

Digital

Microphone

Left/Data1

Digital

Microphone

VANA

VA

0.1 µF

PMU

USB

+5 V

VBAT

LDO

Switching

Regulator

Reset

Generator

+1.8 V

+1.8 V

VDIG

VDIG

VBAT

Class-D

CS35L0x

+

+

1 µF

1 µF

1 µF

0.1 µF

0.1 µF

0.1 µF

0.1 µF

+

+

2.2 µF

2.2 µF