6 adc control - address 06h, 1 dither for 16-bit data (bit 5), 2 adc digital interface format (bit 4) – Cirrus Logic CS4271 User Manual

Page 43: Table 17. adc digital interface formats, 3 adc channel a & b mute (bits 3:2), 7 mode control 2 - address 07h, 1 digital loopback (bit 4), 2 amutec = bmutec (bit 3), Cs4271

CS4271

DS592F1

43

8.6

ADC Control - Address 06h

8.6.1

Dither for 16-Bit Data (Bit 5)

Function:

When set, this bit activates the Dither for 16-Bit Data feature as described in “Dither for 16-Bit Data”

on page 30.

8.6.2

ADC Digital Interface Format (Bit 4)

Function:

The required relationship between LRCK, SCLK and SDOUT for the ADC is defined by the ADC Dig-

ital Interface Format. The options are detailed in Table 17 and may be seen in Figure 3 and 4.

8.6.3

ADC Channel A & B Mute (Bits 3:2)

Function:

When this bit is set, the output of the ADC for the selected channel will be muted.

8.6.4

Channel A & B High Pass Filter Disable (Bits 1:0)

Function:

When this bit is set, the internal high-pass filter for the selected channel will be disabled.The current

DC offset value will be frozen and continue to be subtracted from the conversion result. See “High

Pass Filter and DC Offset Calibration” on page 30.

8.7

Mode Control 2 - Address 07h

8.7.1

Digital Loopback (Bit 4)

Function:

When this bit is set, an internal digital loopback from the ADC to the DAC will be enabled. Please refer

to “Internal Digital Loopback” on page 30.

8.7.2

AMUTEC = BMUTEC (Bit 3)

Function:

When this function is enabled, the individual controls for AMUTEC and BMUTEC are internally con-

nected through an AND gate prior to the output pins. Therefore, the external AMUTEC and BMUTEC

pins will go active only when the requirements for both AMUTEC and BMUTEC are valid.

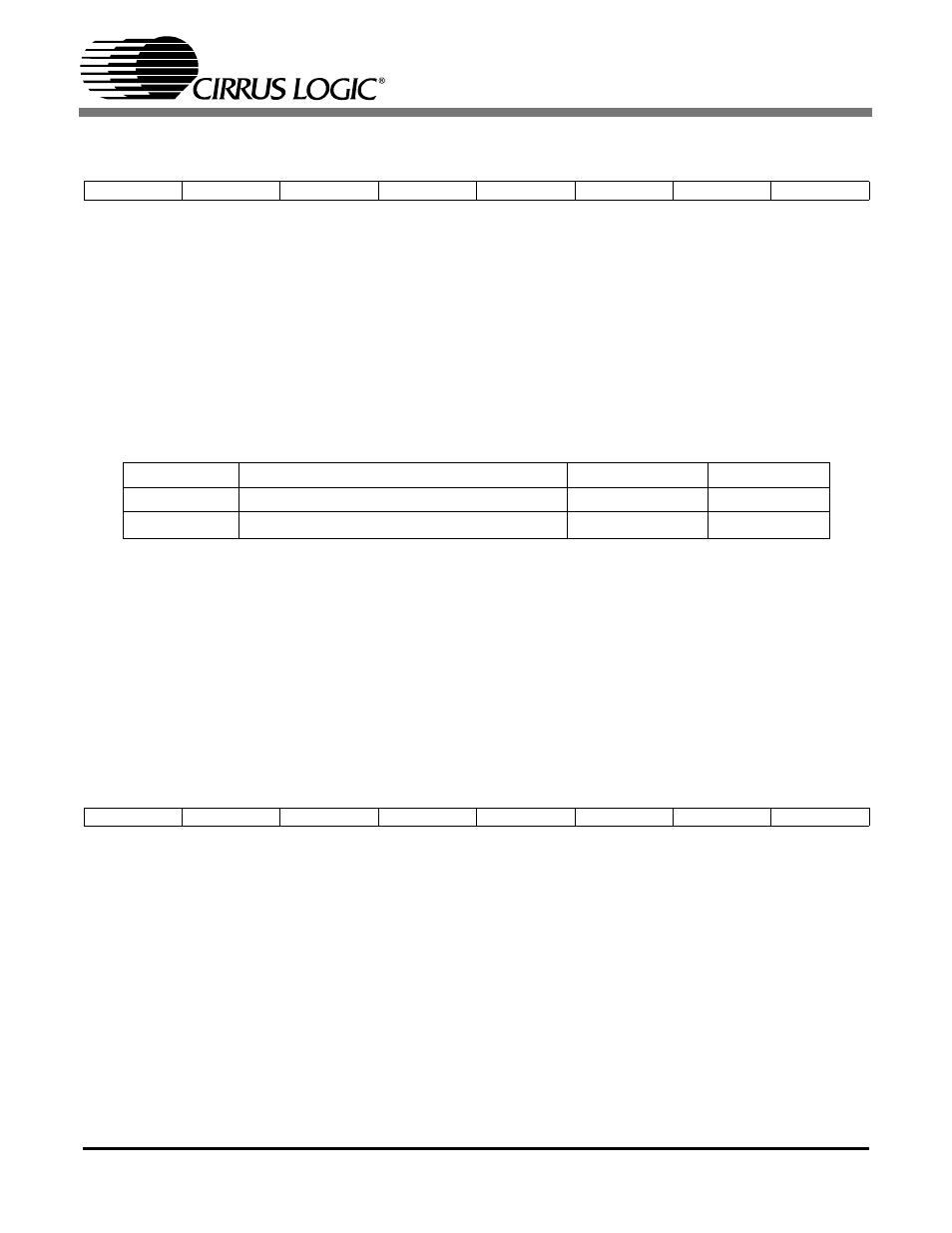

7

6

5

4

3

2

1

0

Reserved

Reserved

Dither16

ADC_DIF

MUTEA

MUTEB

HPFDisableA

HPFDisableB

Table 17. ADC Digital Interface Formats

ADC_DIF

Description

Format

Figure

0

Left Justified, up to 24-bit data (default)

0

1

I

2

S, up to 24-bit data

1

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

LOOP

MUTECA=B

FREEZE

CPEN

PDN