Figure 8. phase locked loop, Figure 8, Optional pll (phase locked loop) – Cirrus Logic CRD4202-1 User Manual

Page 14

CRD4202-1

14

DS549RD1A1

R51

NO POP

C68

NO POP

C69

NO POP

R52

NO POP

R53

NO POP

Y2

NO POP

3

1

2

4

DGND

DGND

+3.3VD

DGND

XT

AL

_

O

U

T

XT

AL

_

IN

ID

1#

ID

0#

1)

2)

3)

4)

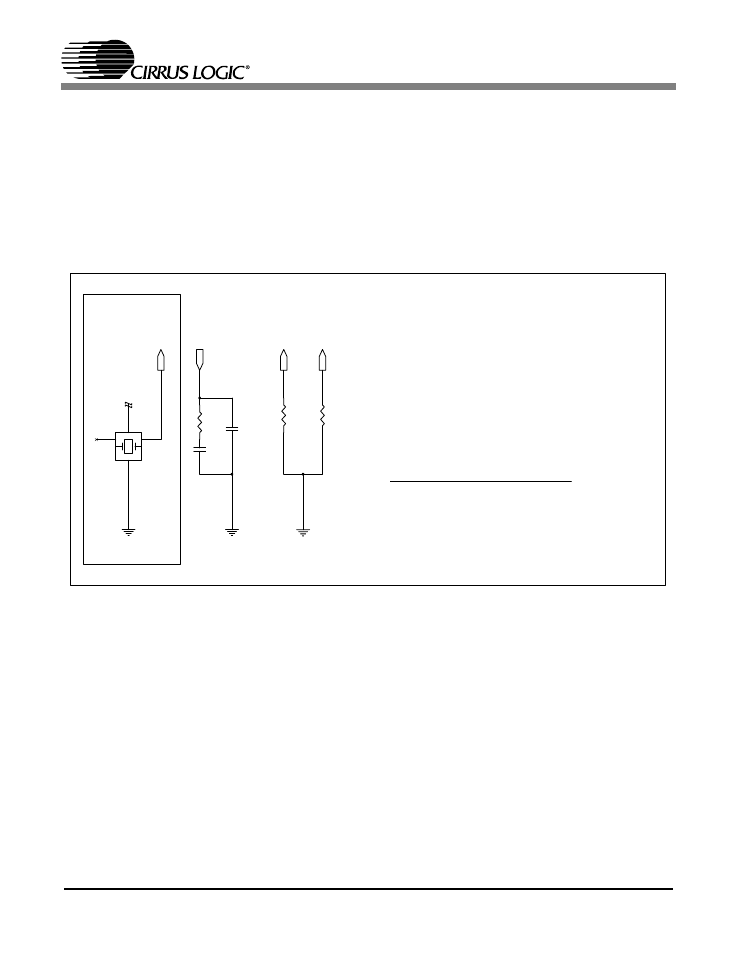

For PLL operation:

OPTIONAL PLL (Phase Locked Loop)

Populate R54 = 1K

DO NOT populate: Y1, C14, C15, and R55

Apply external oscillator to XTAL_IN (pin 2)

(CRD4202-1 can use test oscillator on Y2: ECS-8FA3)

Populate R51, R52, R53, C68, and C69 according to

your input clock rate:

clock rate (MHz)

R51

R52

R53

C68

C69

14.31818

2.2K

NO POP

0 ohm

0.022uF

220pF

24.576

NO POP

NO POP NO POP

NO POP

NO POP

27

2.2K

0 ohm

NO POP

0.022uF

220pF

48

2.2K

0 ohm

0 ohm

0.022uF

220pF

Test Clock Only

Figure 8. Phase Locked Loop

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)