2 reducing the gain with external series resistors, Section 5.1.2.1, Section 5.1.2.2 – Cirrus Logic CS35L03 User Manual

Page 16

CS35L01/03

16

DS909F1

In both HD and FHD mode, the value of the capacitance connected to the LFILT+ pin must not exceed

4.7

F. If this value is greater than 4.7 F, it will prevent the rail voltage of the output devices from transi-

tioning properly between VBATT and the internal LDO.

5.1.2.1

HD Mode

Hybrid Class-D mode (HD) provides competitive analog performance with a substantial reduction in idle

power dissipation and radiation emissions. In this mode, the output switches at 192 kHz and a secondary

supply is derived from VBATT using an internal 1.0-VDC low drop-out linear regulator (LDO). When the

output signal is at a low amplitude, the Class-D output stage begins to switch from the lower rail voltage

created by the internal LDO. This not only decreases idle power consumption when output capacitors are

used, but also reduces electromagnetic emissions by reducing the amplitude of the square waves being

created at the output of the CS35L01/03 when operating at low amplitude or idle power.

5.1.2.2

FHD Mode

The Reduced Frequency Hybrid Class-D (FHD) mode provides the best overall EMI performance and the

lowest power consumption with slightly decreased frequency response near the top frequency range of

the audio band, for high amplitude signals. In this mode of operation, the output switching frequency is

reduced to 76 kHz during high amplitude transients on the output. The threshold at which this transition

from 192-kHz to 76-kHz switching rate occurs is given as the Input Level Threshold for FHD Operation in

“Electrical Characteristics - FHD Mode” on page 13

. Combined with the lower amplitude switching offered

by the Hybrid design, this reduction in switching energy dramatically reduces the emissions levels of the

output stage and its associated components.

5.2

Reducing the Gain with External Series Resistors

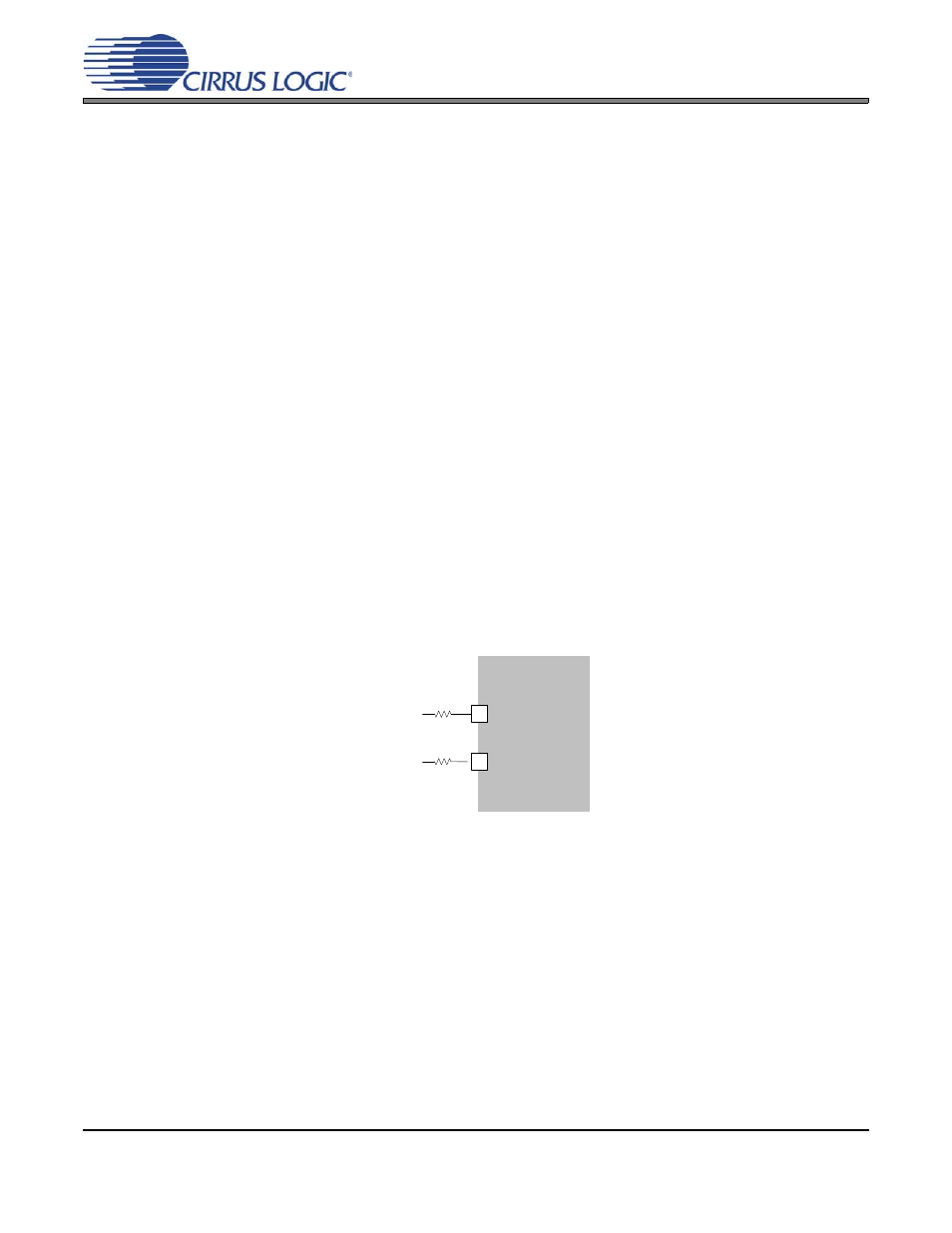

If necessary, it is possible to decrease the gain of the CS35L01/03 by adding series resistors to the audio

input signal as is shown in

below.

If input resistors are added, the new gain of the amplifier can be determined by the following equation:

Where:

A

V(adjusted)

= The new, adjusted gain of the system

Z

IN

= Input impedance of the device being used (See

“Electrical Characteristics - SD Mode” on page 10

,

“Electrical Characteristics - FSD Mode” on page 11

,

“Electrical Characteristics - HD Mode” on page 12

“Electrical Characteristics - FHD Mode” on page 13

for this value.)

Z

EXT

= Value of the resistor added in series with the inputs

Audio In+

Audio In-

R

IN

R

IN

AIN+

AIN-

x

x

Figure 4. Adjusting Gain via External Series Resistance

A

V adjusted

A

V

20

–

Z

IN

Z

IN

Z

EXT

+

--------------------------

log

=