Logic levels, Vih(ac), maximum ac input logic high, Vih(dc), minimum dc input logic high – Teledyne LeCroy QPHY-DDR3 User Manual

Page 37: Qphy-ddr3 software option

QPHY-DDR3 Software Option

917717 Rev C

37

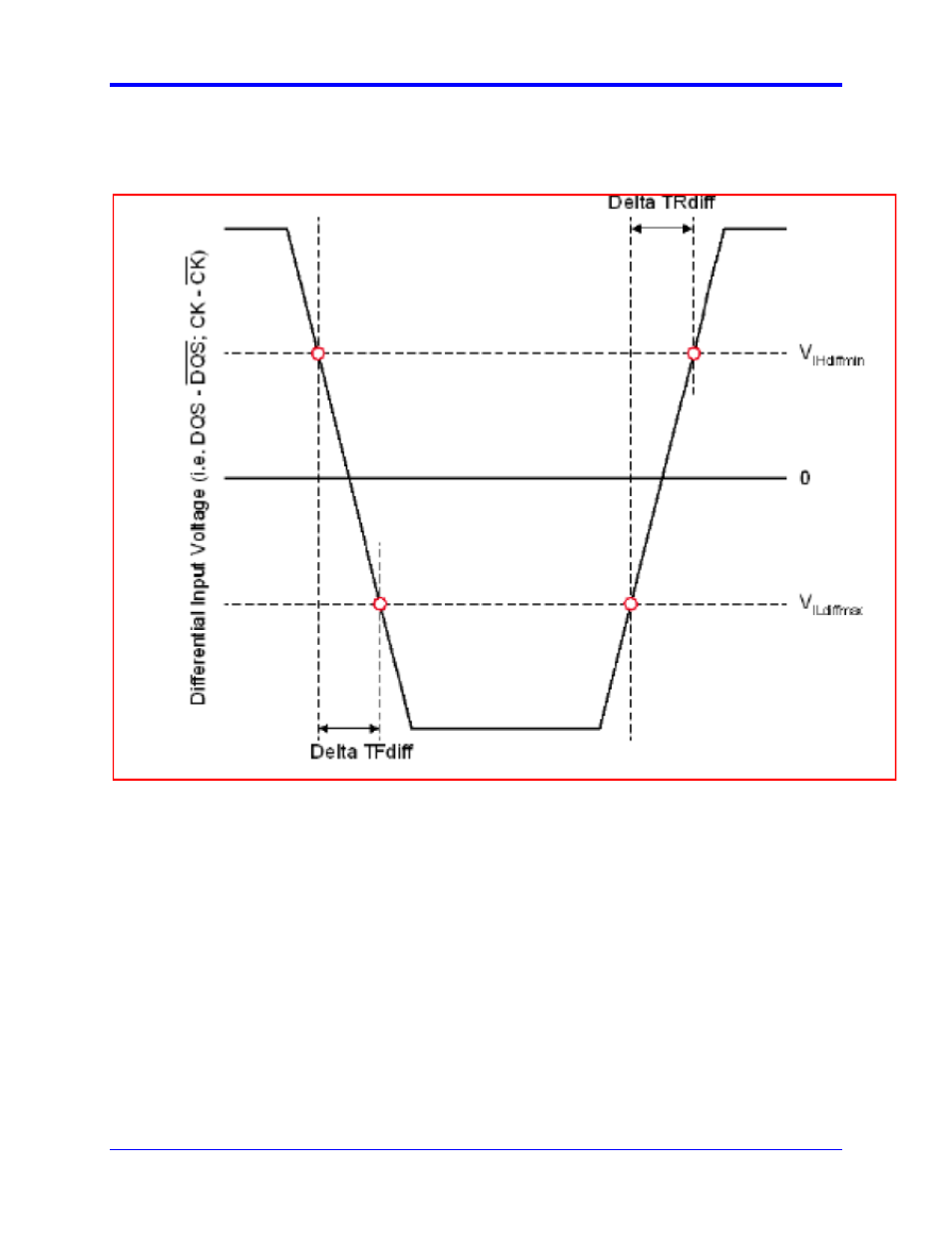

For differential signals (e.g. CK - CK#) slew rate for rising edges is measured from Vihdiffmin to

Vihdiffmax. This test is informational only.

Figure 16. AC input test signal waveform [JESD79-3D figure 94]

Logic Levels

VIH(ac), maximum AC input logic high

Measure the local maximum value from VREF to VREF of the high pulse histogram. If multiple pulses are

measured, take the lowest number and the highest number as the worst cases.

The lowest number must be greater than or equal to the minimum limit and the highest number must be

less than or equal to the maximum limit.

VIH(dc), minimum DC input logic high

Measure the local minimum and maximum values from the first VIH(ac)min crossing point to the time

corresponding to VIH(dc)min crossing a 1V/ns slewrate slope to VREF. If multiple pulses are measured,

take the lowest, respectively the highest, number as the worst case.