Qphy-ddr3 limit sets, Ddr3-800, Ddr3-1066 – Teledyne LeCroy QPHY-DDR3 User Manual

Page 34: Ddr3-1333, Ddr3-1600, Qphy-ddr3 tests, Clock tests, Tck(avg), average clock period, Tck(abs), absolute clock period, Tch(avg), average high pulse width

34

917717 Rev C

QPHY-DDR3 LIMIT SETS

DDR3-800

This corresponds to the JEDEC JESD79-3D DDR3 standard specification limits for 800 MT/s.

DDR3-1066

This corresponds to the JEDEC JESD79-3D DDR3 standard specification limits for 1066 MT/s.

DDR3-1333

This corresponds to the JEDEC JESD79-3D DDR3 standard specification limits for 1333 MT/s..

DDR3-1600

This corresponds to the JEDEC JESD79-3D DDR3 standard specification limits for 1600 MT/s.

QPHY-DDR3 TESTS

Clock Tests

All time measure on clock CK are done at level VREF.

tCK(avg), Average Clock Period

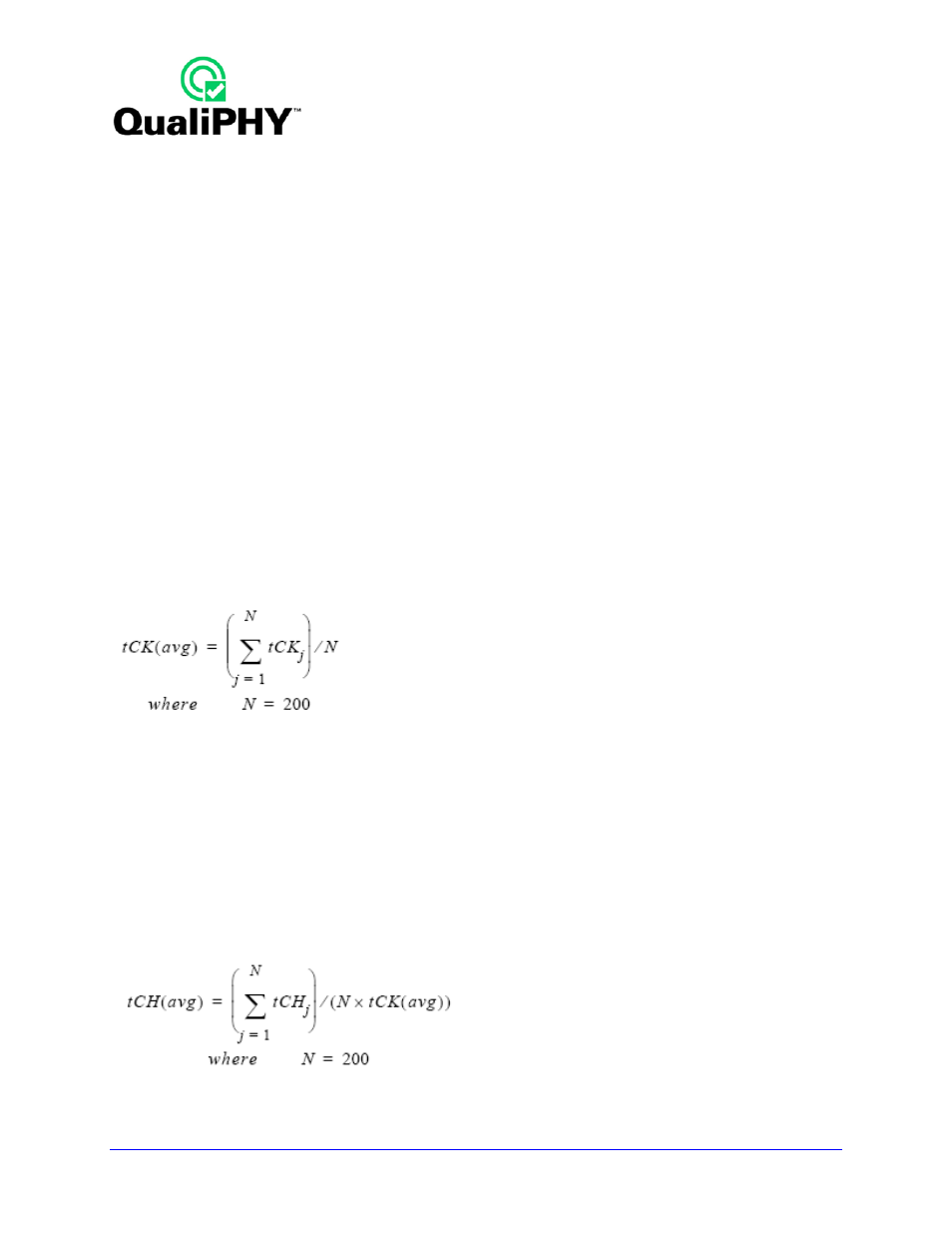

tCK(avg) is calculated as the average clock period across any consecutive 200 cycle window, where each

clock period is calculated from rising edge to rising edge.

tCK(abs), Absolute Clock Period

tCK(abs) is defined as the absolute clock period, as measured from one rising edge to the next

consecutive

rising edge. tCK(abs) is not subject to production test.

tCH(avg), Average High Pulse Width

tCH(avg) is defined as the average high pulse width, as calculated across any consecutive 200 high

pulses.