Pin description, Ddr3 rdimm product specification – SP / Silicon Power SP008GBRTE133M0A User Manual

Page 4

DDR3 RDIMM

Product Specification

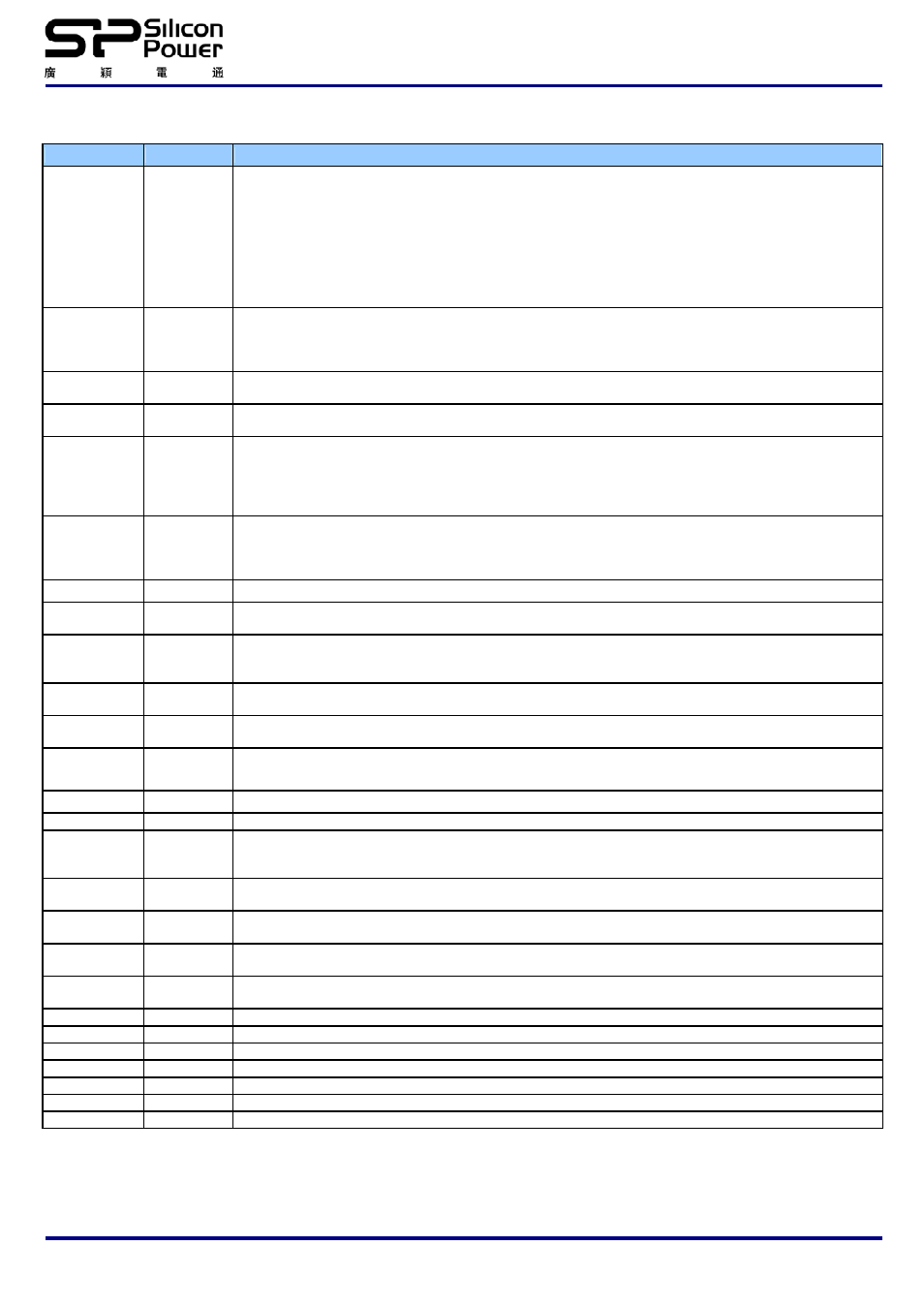

Pin Description

Symbol

Type

Description

A[15:0] Input

Address inputs:

Provide the row address for ACTIVATE commands, and the column

address and auto precharge bit (A10) for READ/WRITE commands, to select one location out

of the memory array in the respective bank. A10 is sampled during a PRECHARGE command

to determine whether the PRECHARGE applies to one bank (A10 LOW, bank selected by

BA[2:0]) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by

BA. A12 is also used for BC4/BL8 identification as “BL on-the-fly” during CAS commands. The

address inputs also provide the op-code during the mode register command set. A[13:0]

address the 1Gb DDR3 devices. A[15:14] are needed to calculate parity on the

command/address bus.

BA[2:0] Input

Bank address inputs:

BA[2:0] define the device bank to which an ACTIVATE, READ,

WRITE, or PRECHARGE command is being applied. BA[2:0] define which mode register

(MR0, MR1, MR2, and MR3) is loaded during the LOAD MODE command. BA[2:0] are used

as part of the parity calculation.

CK0, CK0#

Input

Clock:

CK and CK# are differential clock inputs. All control, command, and address input

signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#.

CKE[1:0] Input

Clock enable:

CKE enables (registered HIGH) and disables (registered LOW) internal

circuitry and clocks on the DRAM.

DM[8:0]

(TDQS[17:9],

TDQS#[17:9])

Input

Input data mask:

DM is an input mask signal for write data. Input data is masked when DM is

sampled HIGH, along with the input data, during a write access. DM is sampled on both edges

of the DQS. Although the DM pins are input-only, the DM loading is designed to match that of

the DQ and DQS pins. When TDQS is enabled, DM is disabled and TDQS and TDQS#

provide termination resistance, otherwise the TDQS# pins are no function.

ODT[1:0] Input

On-die termination:

ODT enables (registered HIGH) and disables (registered LOW)

termination resistance internal to the DRAM. When enabled in normal operation, ODT is

applied only to the following pins: DQ, DQS, DQS#, and DM. The ODT input will be ignored if

disabled via the LOAD MODE command.

Par_In Input

Parity input:

Parity bit for the address, RAS#, CAS#, and WE#.

RAS#, CAS#,

WE#

Input

Command inputs:

RAS#, CAS#, and WE# (along with S#) define the command being

entered.

RESET#

Input

(LVCMOS)

Reset:

RESET# is an active LOW CMOS input referenced to V

SS

. The RESET# input receiver

is a CMOS input defined as a rail-to-rail signal with DC HIGH ≥ 0.8 ×V

DD

and DC LOW ≤ 0.2 ×

V

DD

.

S#[3:0] Input

Chip select:

S# enables (registered LOW) and disables (registered HIGH) the command

decoder.

SA[2:0] Input

Serial address inputs:

These pins are used to configure the temperature sensor/SPD

EEPROM address range on the I2C bus.

SCL Input

Serial clock for temperature sensor/SPD EEPROM:

SCL is used to synchronize

communication to and from the temperature sensor/SPD EEPROM.

CB[7:0] I/O

Check bits:

Data used for ECC.

DQ[63:0] I/O

Data input/output:

Bidirectional data bus.

DQS[8:0],

DQS#[8:0]

I/O

Data strobe:

DQS and DQS# are differential data strobes. Output with read data.

Edge-aligned with read data. Input with write data. Center-aligned with write data. DQS# is

used only when the differential data strobe mode is enabled via the LOAD MODE command.

SDA I/O

Serial data:

SDA is a bidirectional pin used to transfer addresses and data into and out of the

temperature sensor/SPD EEPROM on the module on the I2C bus.

Err_Out#

Output

(open-drain) Parity error output: Parity error found on the command and address bus.

EVENT#

Output

(open-drain)

Temperature event:

The EVENT# pin is asserted by the temperature sensor when critical

temperature thresholds have been exceeded.

V

DD

Supply

Power supply:

1.5V ±0.075V. The component V

DD

and V

DDQ

are connected to the module

V

DD

.

V

DD

SPD Supply

Temperature sensor/SPD EEPROM power supply:

+3.0V to +3.6V.

V

REF

CA Supply

Reference voltage:

Control, command, and address (V

DD

/2).

V

REF

DQ Supply

Reference voltage:

DQ, DM (V

DD

/2).

V

SS

Supply

Ground.

V

TT

Supply

Termination voltage:

Used for control, command, and address (V

DD

/2).

NC –

No connect:

These pins are not connected on the module.

NU –

Not used:

These pins are not used in specific module configuration/operations.

Rev. 1.1 Aug. 2011

4