Pin description, Ddr2 udimm with ecc product specification – SP / Silicon Power SP002GBLRE800S01 User Manual

Page 4

DDR2 UDIMM with ECC

Product

Specification

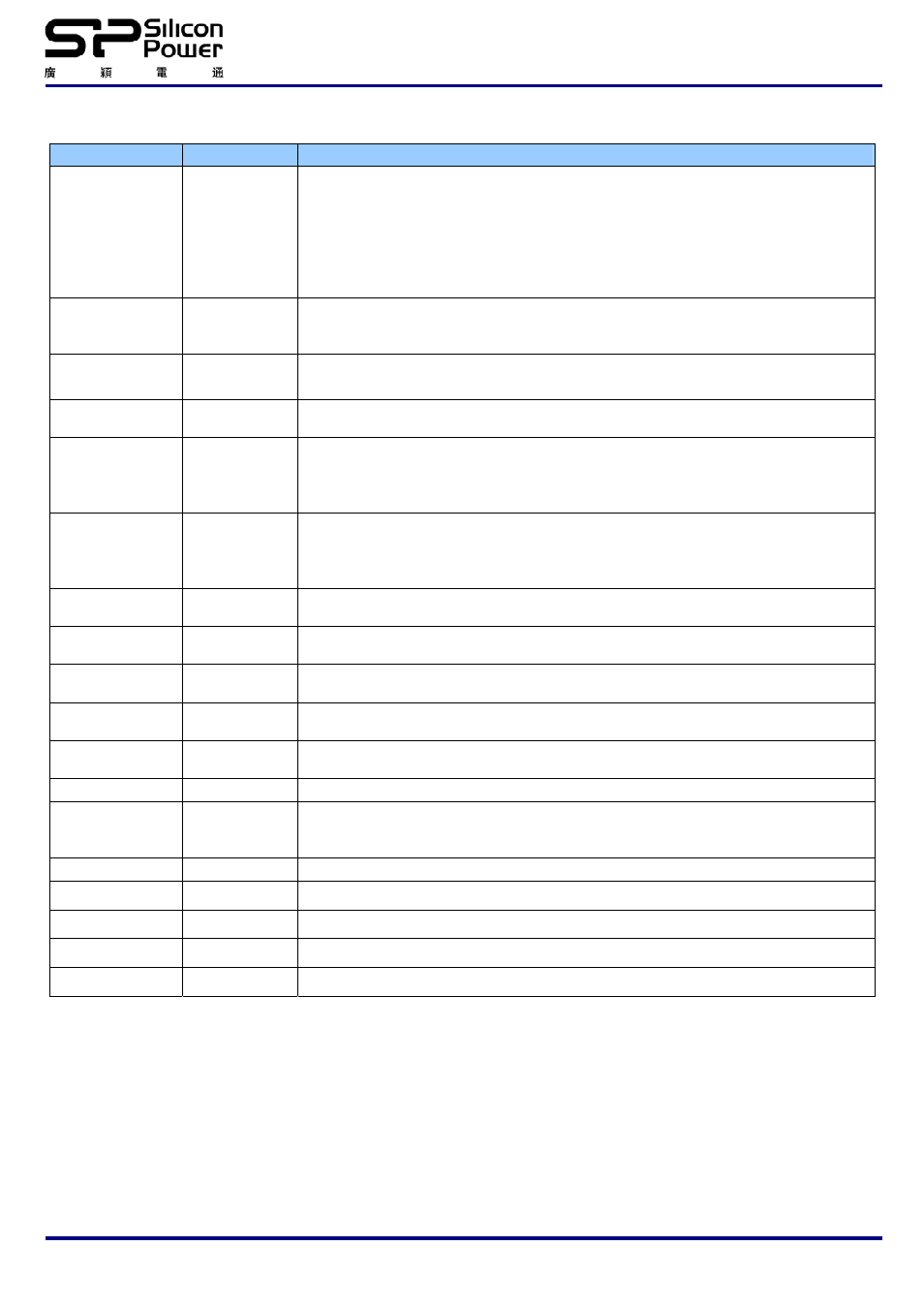

Pin Description

Symbol

Type

Description

Ax

Input

Address inputs: Provide the row address for ACTIVE commands, and the column

address and auto precharge bit (A10) for READ/WRITE commands, to select one

location out of the memory array in the respective bank. A10 sampled during a

PRECHARGE command determines whether the PRECHARGE applies to one

bank (A10 LOW, bank selected by BAx) or all banks (A10 HIGH). The address

inputs also provide the op-code during a LOAD MODE command. See the Pin

Assignments Table for density-specific addressing information.

BAx

Input

Bank address inputs: Define the device bank to which an ACTIVE, READ, WRITE,

or PRECHARGE command is being applied. BA define which mode register (MR0,

MR1, MR2, and MR3) is loaded during the LOAD MODE command.

CKx,

CKx#,

Input

Clock: Differential clock inputs. All control, command, and address input signals are

sampled on the crossing of the positive edge of CK and the negative edge of CK#.

CKEx Input

Clock enable: CKE (registered HIGH) activates and CKE (registered LOW)

deactivates clocking circuitry on the DDR2 SDRAM.

DMx

I/O

Data input mask (x8 devices only): DM is an input mask signal for write data.

Input data is masked when DM is sampled HIGH, along with that input data, during

a write access. DM is sampled on both edges of DQS. Although DM pins are

input-only, the DM loading is designed to match that of DQ and DQS pins.

ODTx Input

On-die termination: ODT (registered HIGH) enables termination resistance

internal to the DDR2 SDRAM. When enabled, ODT is only applied to the following

pins: DQ, DQS, DQS#, and CB. The ODT input will be ignored if disabled via the

LOAD MODE command.

RAS#, CAS#,

WE#

Input

Command inputs: RAS#, CAS#, and WE# (along with S#) define the command

being entered.

Sx#, Sx#

Input

Chip select: Enables (registered LOW) and disables (registered HIGH) the

command decoder.

SAx

Input

Serial address inputs: Used to configure the SPD EEPROM address range on the

I

2

C bus.

SCL

Input

Serial clock for SPD EEPROM: Used to configure the SPD EEPROM address

range on the I

2

C bus.

SDA

I/O

Serial presence-detect data: SDA is a bidirectional pin used to transfer addresses

and data into and out of the presence-detect portion of the module.

DQx

I/O

Data input/output: Bidirectional data bus.

DQSx,

DQSx#

I/O

Data strobe: Output with read data, input with write data for source synchronous

operation. Edge-aligned with read data, center-aligned with write data. DQS# is only

used when differential data strobe mode is enabled via the LOAD MODE command.

V

DD

/V

DDQ

Supply

Power supply: 1.8V ±0.1V.

V

DDSPD

Supply

Serial EEPROM positive power supply: +1.7V to +3.6V.

V

REF

Supply

SSTL_18 reference voltage. (VDD/2)

V

SS

Supply

Ground.

NC

–

No connect: These pins are not connected on the module.

Rev. 1.2 Aug. 2011

4