Anritsu MG3700A User Manual

Page 19

19

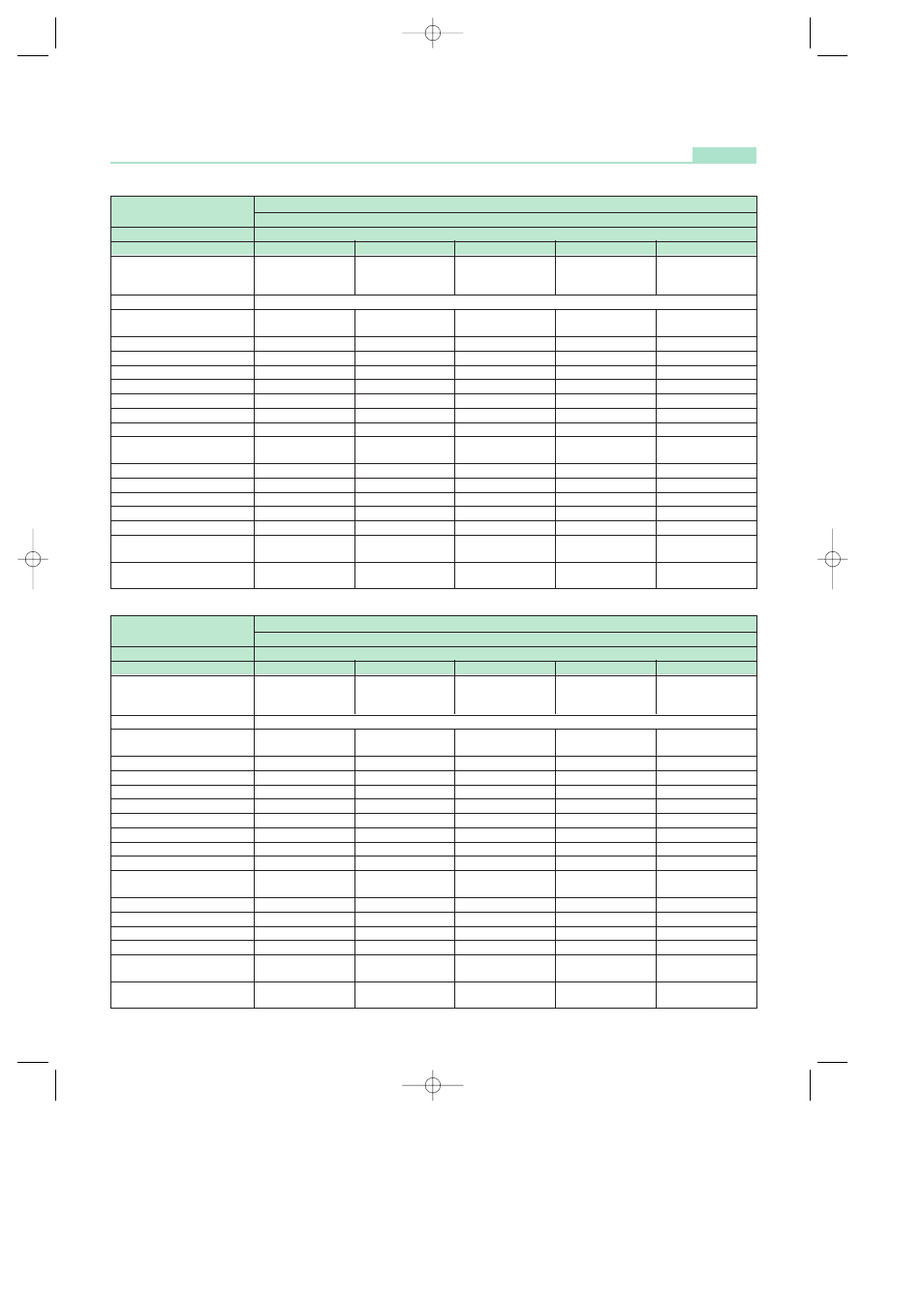

Target of test

BS Receive Test (UL)

BS

Test signal

BS-UL RMC

Waveform patterns

rmc12_2k_bs_ul

rmc12k_ocns_bs_ul

rmc64k_ocns_bs_ul

rmc144k_bs_ul

rmc384k_bs_ul

RS / Min. Input Lev./

Test

Dynamic range /ACS /

Performance Req.

Performance Req.

Performance Req.

Performance Req.

Blocking / Rx IM

Standard

TS25.142

DwPTS/UpPTS/SYNC_DL/UL

NUMBER (quadruples)

—

—

—

—

—

P-CCPCH

—

—

—

—

—

Scrambling Code

0

0

0

0

0

midamble ID

0

0

0

0

0

Maximum User (user number)

2 (1)

2 (1)

2 (1)

2 (1)

2 (1)

Spread Factor

8

8

2, 8

2, 8

8, 2

Time Slot Number

1

1

1

1, 2

1, 2, 3, 4

Number of DPCH

0

4

1

1

0

DPCH Channelization Codes

C (i, 8), i = 1

C (i, 8), i = 1

C (i, 2), i = 1

C (i, 2), i = 1

C (i, 2) i = 1

C (i, 8) i = 5

DPCH0 Channelization Codes

—

C (i, 8), 2

≤

i

≤

5

C (i, 8), i = 5

C (i, 8), i = 5

—

Data: DPCH0

PN9

PN9

PN9

PN9

PN9

Data: other channel

—

PN9

PN9

PN9

—

∑

DPCH_Ec/Ior [dB]

0

—

—

—

0

DPCH0_Ec/Ior [dB]

—

–7

–7

–7

—

DPCH Channelization Codes

0

–7

–0.97

–0.97

C (i, 2) = –6.99

Power [dB] / 1 ch

C (i, 8) = –0.97

DPCH0 Channelization Codes

Power [dB] / 1 ch

—

–7

–7

–7

—

•

Waveform patterns for evaluating BS receivers

Target of test

UE Receiver Test (DL)

UE

Test signal

UE-DL RMC

Waveform pattern

rmc12_2k_ue_dl

rmc12k_ocns_ue_dl

rmc64k_ocns_ue_dl rmc144k_ocns_ue_dl

rmc384k_ue_dl

RS / Min. Input Lev. / Maximum input level

Test

ACS / Blocking /

test / RMC 12.2k

Performance Req.

Performance Req.

Performance Req.

Spur.Resp. / Inter Mod

Standard

TS25.102

DwPTS/UpPTS SYNC_DL/UL

SYNC_DL #0

SYNC_DL #0

SYNC_DL #0

SYNC_DL #0

SYNC_DL #0

NUMBER (quadruples)

(S1)

(S1)

(S1)

(S1)

(S1)

P-CCPCH

Add

Add

Add

Add

Add

Scrambling Code

0

0

0

0

0

midamble ID

0

0

0

0

0

Maximum User (user number)

8 (1)

8 (1)

8 (1)

8 (1)

8 (1)

Spread Factor

16

16

16

16

16

Time Slot Number

4

4

4

4, 5

3, 4, 5, 6

Number of DPCH0

0

8

2

2

0

DPCH Channelization Codes

C (i, 16), i = 1, 2

C (i, 16), i = 1, 2

C (i, 16), i = 1,…, 8

C (i, 16), i = 1,…, 8

C (i, 16)i = 1,…, 10

DPCH0 Channelization Codes

—

C (i, 16)

C (i, 16)

C (i, 16)

—

3

≤

i

≤

10

9

≤

i

≤

10

9

≤

i

≤

10

Data:DPCH0

PN9

PN9

PN9

PN9

PN9

Data: other channel

—

PN9

PN9

PN9

—

∑

DPCH_Ec/Ior [dB]

0

–7

—

—

—

DPCH0_Ec/Ior [dB]

—

–10

–10

–10

0

DPCH Channelization Codes

Power [dB] / 1ch

–3.01

–10.00

–10.00

–10.00

–10

DPCH0 Channelization Codes

Power [dB / 1 ch

—

–10.00

–10.00

–10.00

—

•

Waveform patterns for evaluating receiver of UE

MX370001A TD-SCDMA waveform pattern

Optional

*MX370X_E_050127 1/28/05 8:51 AM Page 19