Phs waveform pattern – Anritsu MG3700A User Manual

Page 12

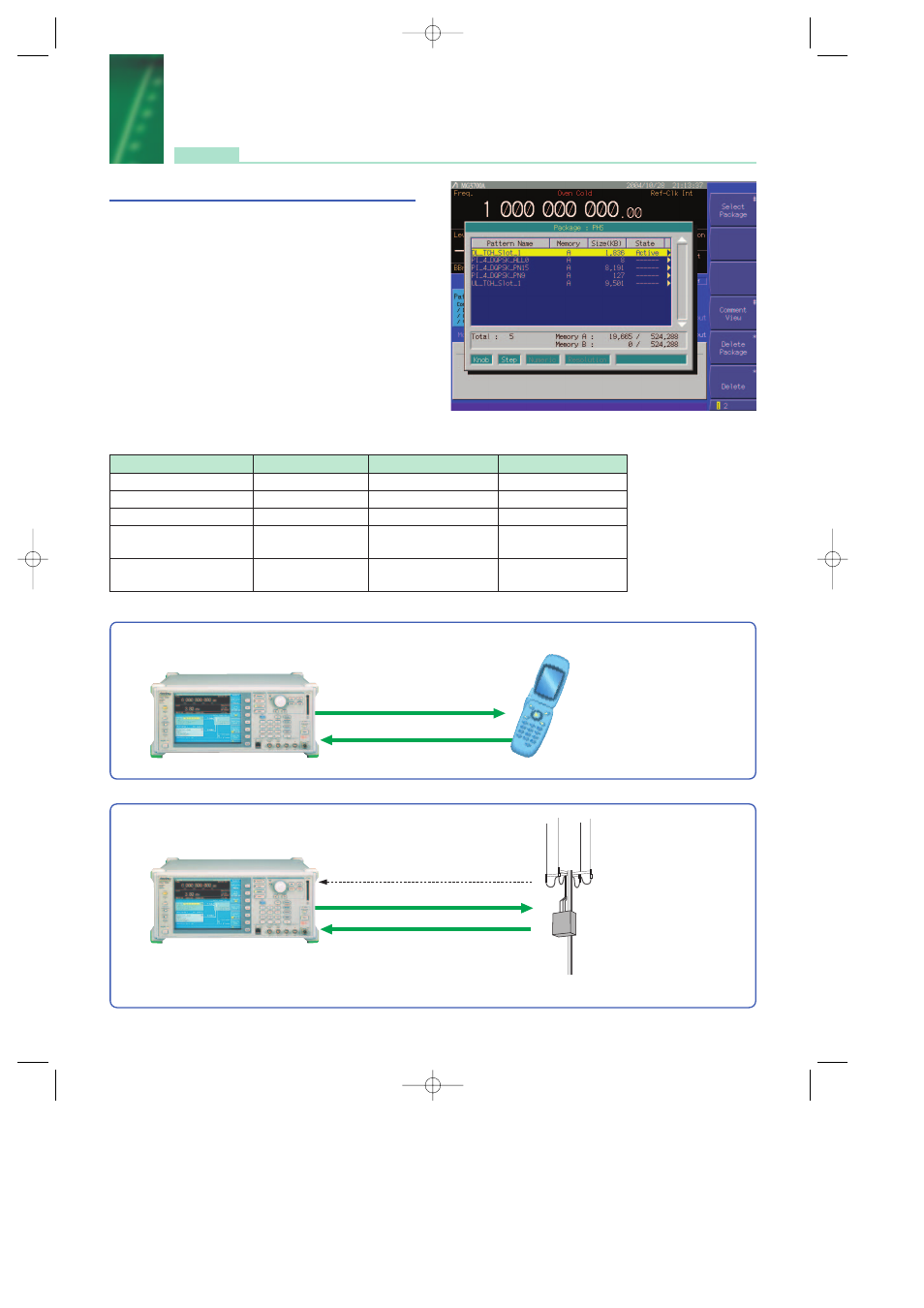

Waveform pattern

Uplink / Downlink

Scramble

Output slot

PI_4_DQPSK_PN9

—

OFF No

frame

PI_4_DQPSK_PN15

—

OFF

No frame

PI_4_DQPSK_ALL0

—

OFF

No frame

DL_TCH_Slot_1

Uplink /

Downlink

OFF

Slot1: TCH

Slot 2 to 4: off

UL_TCH_Slot_1 Uplink

/ Downlink

OFF

Slot1: TCH

Slot 2 to 4: off

12

PHS waveform pattern

Standard

■

PHS waveform pattern:

The PHS waveform patterns listed in the table below are

provided on the MG3700A internal hard disk.

The signals for testing CS (base station) and PS (mobile station)

receivers, which are specified in RCR STD-28, can be output

by selecting one of these PHS waveform patterns, without

setting any complex RCR STD-28 parameters.

When a signal that has parameters different from those of the

provided waveform patterns are required, parameter setting

and waveform pattern generation are available using the

optional MX370102A TDMA IQproducer.

Example of selecting waveform pattern

•

PS receiver test

MG3700A Vector Signal Generator

Modulation signal (Downlink)

Data, Clock

BER analyzer is built in.

PS

CS

•

PS receiver test

MG3700A Vector Signal Generator

BER analyzer is built in.

Modulation signal (Uplink)

Data, Clock

Trigger

∗

∗

Trigger: Timing for synchronizing frames (frame trigger)

*MX370X_E_050127 1/28/05 8:51 AM Page 12