Pam2325, Application information – Diodes PAM2325 User Manual

Page 9

PAM2325

Document number: DSxxxxx Rev. 2 - 0

9 of 12

January 2013

© Diodes Incorporated

PAM2325

A Product Line of

Diodes Incorporated

Application Information

(cont.)

Thermal Consideration (cont.)

Since R

DS(ON)

, quiescent current, and switching losses all vary with input voltage, the total losses should be investigated over the complete input

voltage range. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surrounding airflow

and temperature difference between junction and ambient. The maximum power dissipation can be calculated by the following formula:

θ

−

=

JA

A

)

MAX

(

J

D

T

T

P

Where T

J(MAX)

is the maximum allowable junction temperature 125°C.T is the ambient temperature and θ

JA

is the thermal resistance from the

junction to the ambient. Based on the standard JEDEC for a two layer thermal test board, the thermal resistance θ

JA

of QFN2X2-12 80°C/W

respectively. The maximum power dissipation at T

A

= +25°C can be calculated by following formula:

P

D

= (125°C - 25°C) /80°C/W = 1.25W

Setting the Output Voltage

The internal reference is 0.6V (Typical). The output voltage is calculated as below:

The output voltage is given by Table 1.

⎟

⎠

⎞

⎜

⎝

⎛ +

=

2

R

1

R

1

x

6

.

0

V

O

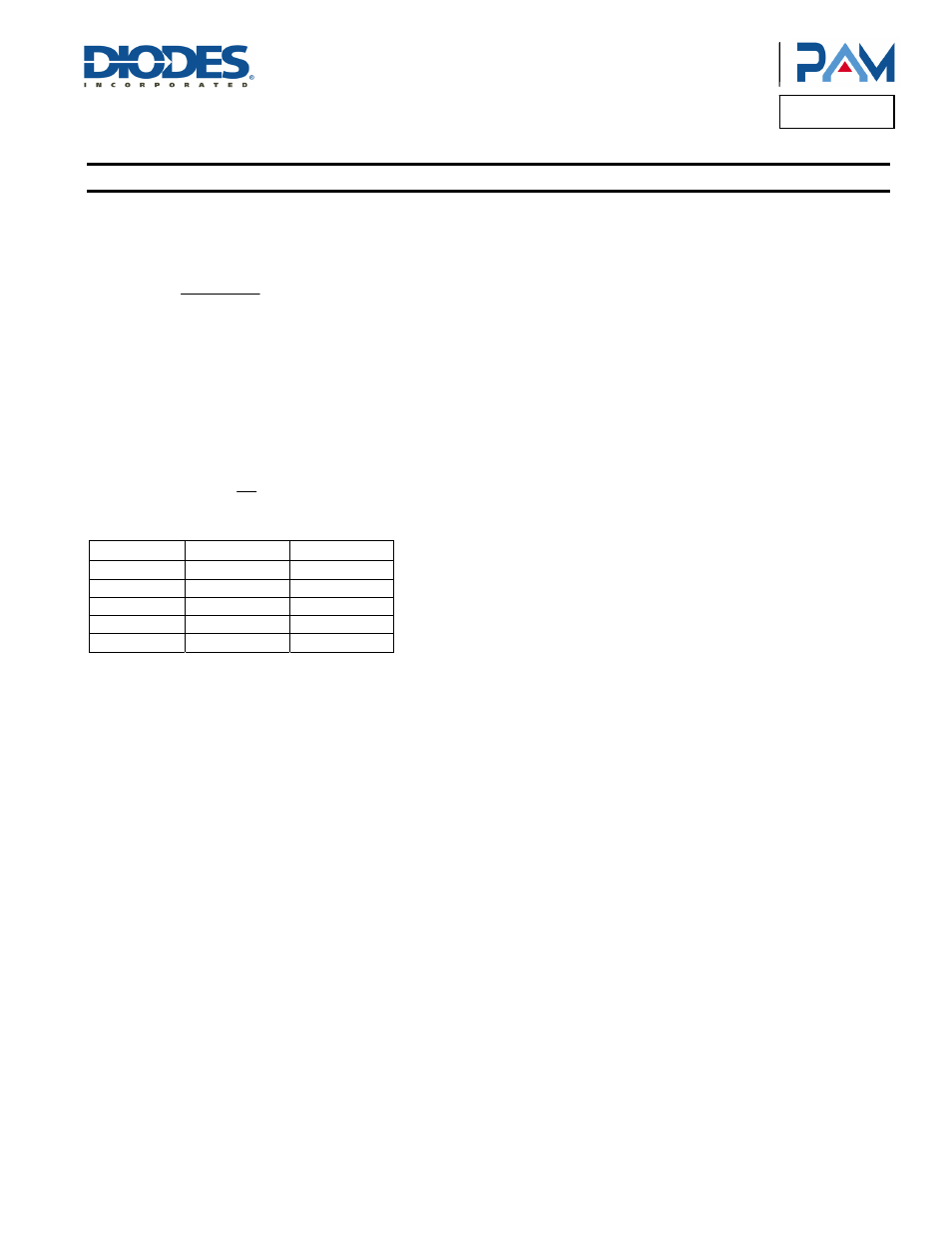

Table 1: Resistor selection for output voltage setting.

V

O

R1 R2

1.2V 150k 150k

1.5V 150k 100k

1.8V 300k 150k

2.5V 380k 120k

3.3V 680k 150k

Pulse Skipping Mode (PSM) Description

When load current decreases, the peak switch current in Power-PMOS will be lower than skip current threshold and the device will enter into

Pulse Skipping Mode.

In this mode, the device has two states, working state and idle state. First, the device enters into working state control led by internal error

amplifier.When the feedback voltage gets higher than internal reference voltage, the device will enter into low I idle state with most of internal

blocks disabled. The output voltage will be reduced by loading or leakage current. When the feedback voltage gets lower than the internal

reference voltage, the convertor will start a working state again.

100% Duty Cycle Operation

As the input voltage approaches the output voltage, the converter turns the P-Channel transistor continuously on. In this mode the output voltage

is equal to the input voltage minus the voltage drop across the P-Channel transistor:

(

)

R

R

I

V

V

L

DSON

LOAD

IN

OUT

+

−

=

where R

DS(ON)

= P-Channel switch ON resistance, I

LOAD

= Output current, R

L

= Inductor DC resistance.

UVLO and Soft-Start

The reference and the circuit remain reset until the V

IN

crosses its UVLO threshold. The PAM2325 has an internal soft-start circuit that limits the

in-rush current during start-up.

This prevents possible voltage drops of the input voltage and eliminates the output voltage overshoot.

Hiccup Mode Short Circuit Control

When the converter output is shorted or the device is overloaded,each high-side MOSFET current- limit event turns off the high-side MOSFET and

turns on the low-side MOSFET. An internal counter is used to count the each current-limit event. The counter is reset after consecutive high-side

MOSFETs turn on without reaching current limit. If the current- limit condition persists, the counter fills up. The control logic then stops both high-

side and lowside MOSFETs and waits for a hiccup period, before attemping a new soft-start sequence. The counter bit is decided by V

FB

voltage.

If V

FB

≤ 0 2, the counter is 3-bit counter; if V

FB

>0.2 the counter is 6-bit counter. The typical hicuup made duty cycle is 1.7%. The hicuup mode is

disable during soft-start time.