Maximum ratings, Thermal characteristics, Electrical characteristics – Diodes DMP2006UFG User Manual

Page 2

POWERDI is a registered trademark of Diodes Incorporated

DMP2006UFG

Document number: DS36802 Rev. 2 - 2

2 of 6

April 2014

© Diodes Incorporated

DMP2006UFG

ADVAN

CE I

N

F

O

RM

ATI

O

N

ADVAN

CE I

N

F

O

RM

ATI

O

N

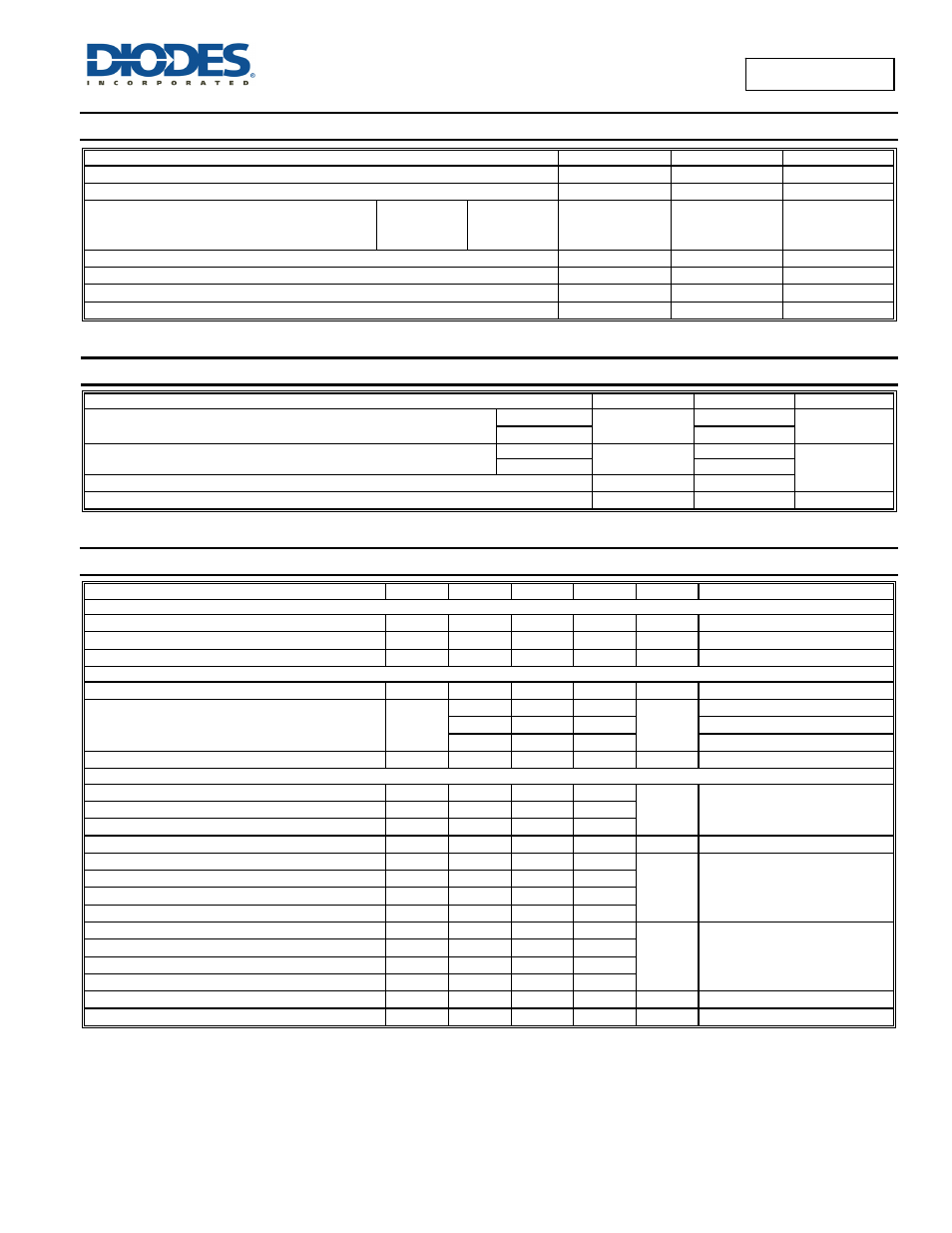

Maximum Ratings

(@T

A

= +25°C, unless otherwise specified.)

Characteristic Symbol

Value

Units

Drain-Source Voltage

V

DSS

-20 V

Gate-Source Voltage (Note 5)

V

GSS

±10 V

Continuous Drain Current (Note 6) V

GS

= -4.5V

Steady

State

T

A

= +25°C

T

A

= +70°C

T

C

= +25°C

I

D

-17.5

-14.0

-40

A

Pulsed Drain Current (10μs pulse, duty cycle = 1%)

I

DM

-80 A

Maximum Continuous Body Diode Forward Current (Note 6)

I

S

-2.2 A

Avalanche Current (Note 8) L=0.1mH

I

AS

-23 A

Avalanche Energy (Note 8) L=0.1mH

E

AS

28 mJ

Thermal Characteristics

(@T

A

= +25°C, unless otherwise specified.)

Characteristic Symbol

Value

Units

Total Power Dissipation (Note 6)

T

A

= +25°C

P

D

2.3

W

T

C

= +25°C

41

Thermal Resistance, Junction to Ambient

(Note 6)

R

θJA

54

°C/W

(Note 7)

136

Thermal Resistance, Junction to Case (Note 6)

R

θJC

3.0

Operating and Storage Temperature Range

T

J,

T

STG

-55 to +150

°C

Electrical Characteristics

(@T

A

= +25°C, unless otherwise specified.)

Characteristic Symbol

Min

Typ

Max

Unit

Test

Condition

OFF CHARACTERISTICS (Note 9)

Drain-Source Breakdown Voltage

BV

DSS

-20 — — V

V

GS

= 0V, I

D

= -250µA

Zero Gate Voltage Drain Current

I

DSS

— — -1

µA

V

DS

= -16V, V

GS

= 0V

Gate-Source Leakage

I

GSS

— —

±100

nA

V

GS

=

8V, V

DS

= 0V

ON CHARACTERISTICS (Note 9)

Gate Threshold Voltage

V

GS(th)

-0.4 — -1.0 V

V

DS

= V

GS

, I

D

= -250µA

Static Drain-Source On-Resistance

R

DS (ON)

— 4.2 5.2

mΩ

V

GS

= -4.5V, I

D

= -15A

— 5.4 7.5

V

GS

= -2.5V, I

D

= -10A

— 7 —

V

GS

= -1.8V, I

D

= -1A

Diode Forward Voltage

V

SD

— -0.7 -1.2 V

V

GS

= 0V, I

S

= -10A

DYNAMIC CHARACTERISTICS (Note 10)

Input Capacitance

C

iss

— 5404 —

pF

V

DS

= -10V, V

GS

= 0V

f = 1.0MHz

Output Capacitance

C

oss

—

728

—

Reverse Transfer Capacitance

C

rss

—

612

—

Gate Resistance

R

G

—

3.8

—

Ω

V

DS

= 0V, V

GS

= 0V, f = 1.0MHz

Total Gate Charge (V

GS

= -4.5V)

Q

g

—

64

—

nC

V

DD

= -10V, I

D

= -20A

Total Gate Charge (V

GS

= -10V)

Q

g

—

140

—

Gate-Source Charge

Q

gs

—

8.5

—

Gate-Drain Charge

Q

gd

—

17

—

Turn-On Delay Time

t

D(on)

—

9.1

—

ns

V

GS

= -4.5V, V

DD

= -10V,

R

G

= 1Ω, R

G

= 1Ω

I

D

= -10A

Turn-On Rise Time

t

r

—

19

—

Turn-Off Delay Time

t

D(off)

—

146

—

Turn-Off Fall Time

t

f

—

104

—

Reverse Recovery Time (Note 10)

t

rr

—

61

— ns

I

F

= -10A, di/dt = 100A/µs

Reverse Recovery Charge (Note 10)

Q

rr

—

44

— nC

I

F

= -10A, di/dt = 100A/µs

Notes:

5. AEC-Q101 VGS maximum is ±8V

6. R

θJA

is determined with the device mounted on FR-4 substrate PC board, 2oz copper, with 1inch square copper plate. R

θJC

is guaranteed by design

while R

θJA

is determined by the user’s board design.

7. Device mounted on FR-4 substrate PC board, 2oz copper, with minimum recommended pad layout.

8 .UIS in production with L =0.1mH, T

J

= +25°C

9. Short duration pulse test used to minimize self-heating effect.

10. Guaranteed by design. Not subject to product testing.