Electrical characteristics – Diodes AP2161/ AP2171 User Manual

Page 4

AP2161/ AP2171

Document number: DS31564 Rev. 7 - 2

4 of 18

March 2013

© Diodes Incorporated

AP2161/ AP2171

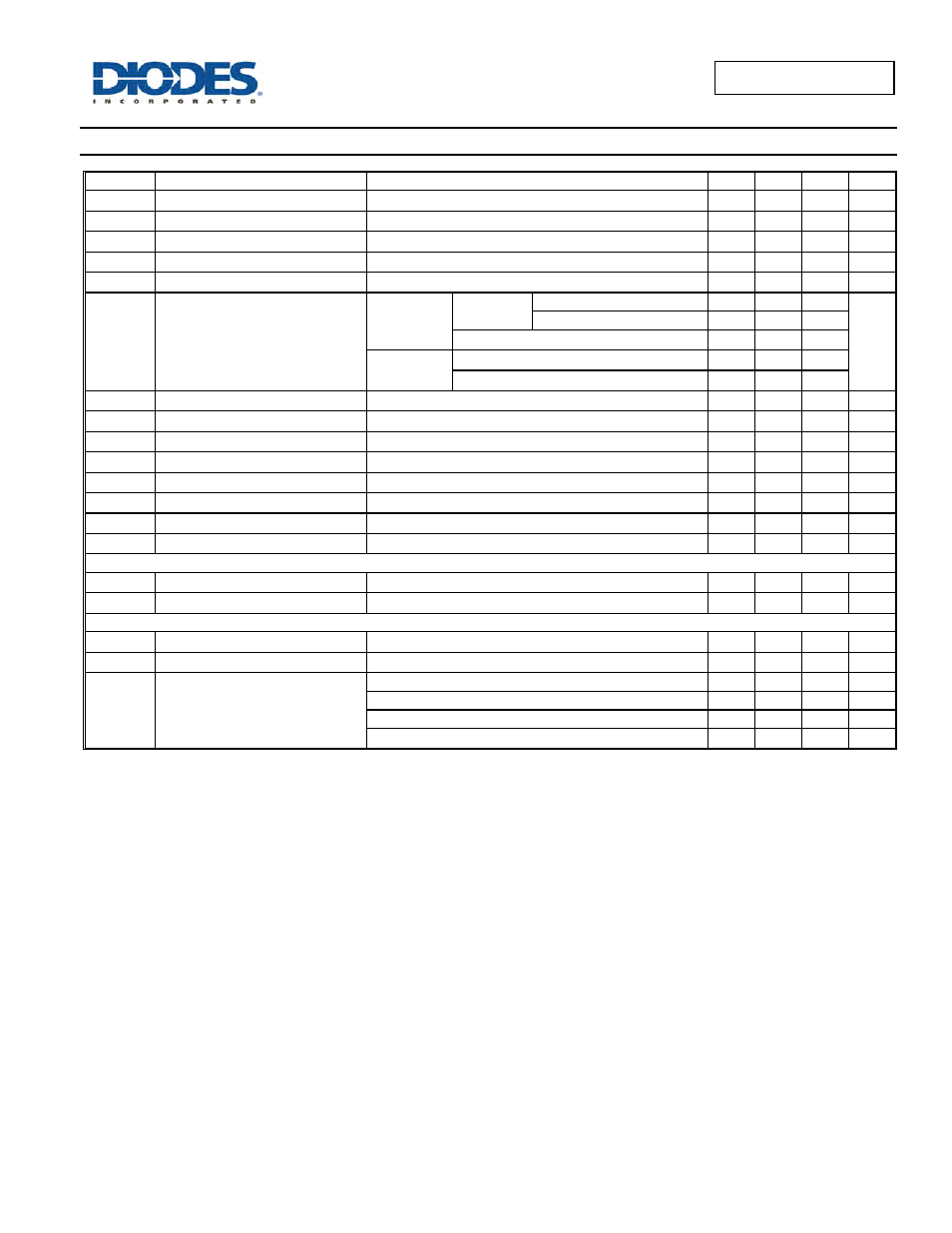

Electrical Characteristics

(@T

A

= +25°C, V

IN

= +5V, unless otherwise specified.)

Symbol Parameter

Test

Conditions

Min

Typ

Max

Unit

V

UVLO

Input UVLO

R

LOAD

= 1k

Ω

1.6 1.9 2.5 V

I

SHDN

Input Shutdown Current

Disabled, I

OUT

= 0

0.5 1 A

I

Q

Input Quiescent Current

Enabled, I

OUT

= 0

45

70

µA

I

LEAK

Input Leakage Current

Disabled, OUT grounded

1

µA

I

REV

Reverse Leakage Current

Disabled, V

IN

= 0V, V

OUT

= 5V, I

REV

at V

IN

1 µA

R

DS(ON)

Switch on-resistance

V

IN

= 5V,

I

OUT

= 1A

T

A

= +25°C

SOT25, MSOP-8EP, SO-8

95

115

m

Ω

U-DFN2018-6

90

110

-40°C

≤ T

A

≤ +85°C

140

V

IN

= 3.3V,

I

OUT

= 1A

T

A

= +25°C

120

140

-40°C

≤ T

A

≤ +85°C

170

I

SHORT

Short-Circuit Current Limit

Enabled into short circuit, C

L

= 68µF

1.2 A

I

LIMIT

Over-Load Current Limit

V

IN

= 5V, V

OUT

= 4.6V, C

L

= 68µF, -40°C

≤ T

A

≤ +85°C

1.1 1.5 1.9 A

I

Trig

Current limiting trigger threshold

Output Current Slew rate (<100A/s) , C

L

=68µF

2.0 A

I

SINK

EN Input leakage

V

EN

= 5V

1

µA

t

D(ON)

Output turn-on delay time

C

L

= 1µF, R

LOAD

= 10

Ω

0.05 ms

t

R

Output turn-on rise time

C

L

= 1µF, R

LOAD

= 10

Ω

0.6

1.5

ms

t

D(OFF)

Output turn-off delay time

C

L

= 1µF, R

LOAD

= 10

Ω

0.01 ms

t

F

Output turn-off fall time

C

L

= 1µF, R

LOAD

= 10

Ω

0.05

0.1 ms

Fault Flag

R

FLG

FLG output FET on-resistance

I

FLG

= 10mA

20

40

Ω

t

Blank

FLG blanking time

C

IN

= 10µF, C

L

= 68µF

4 7 15

ms

Over-Temperature Protection

T

SHDN

Thermal Shutdown Threshold

Enabled, R

LOAD

= 1k

Ω

140

C

T

HYS

Thermal

Shutdown

Hysteresis

25

C

θ

JA

Thermal Resistance Junction-to-

Ambient

SO-8 (Note 5)

110

°C/W

MSOP-8EP (Note 6)

60

°C/W

SOT25 (Note 7)

157

°C/W

U-DFN2018-6 (Note 8)

70

°C/W

Notes:

5. Test condition for SO-8: Device mounted on FR-4, 2oz copper, with minimum recommended pad layout.

6. Test condition for MSOP-8EP: Device mounted on 2” x 2” FR-4 substrate PC board, 2oz copper, with minimum recommended pad on top layer and

thermal vias to bottom layer ground plane.

7. Test condition for SOT25: Device mounted on FR-4, 2oz copper, with minimum recommended pad layout.

8. Test condition for U-DFN2018-6: Device mounted on FR-4 2-layer board, 2oz copper, with minimum recommended pad on top layer and 3 vias to bottom

layer 1.0”x1.4” ground plane.