Zxld1615 – Diodes ZXLD1615 User Manual

Page 7

APPLICATIONS

Setting output voltage

The ZXLD1615 has an adjustable output voltage

allowing the end user maximum flexibility. To set the

output voltage a potential divider network is needed

(see R1 and R2 in typical applications circuit).

The output voltage is determined by the equation:

V

V

R

R

OUT

FB

=

+

⎛

⎝

⎜

⎞

⎠

⎟

1

2

1

where VFB = 1.025V.

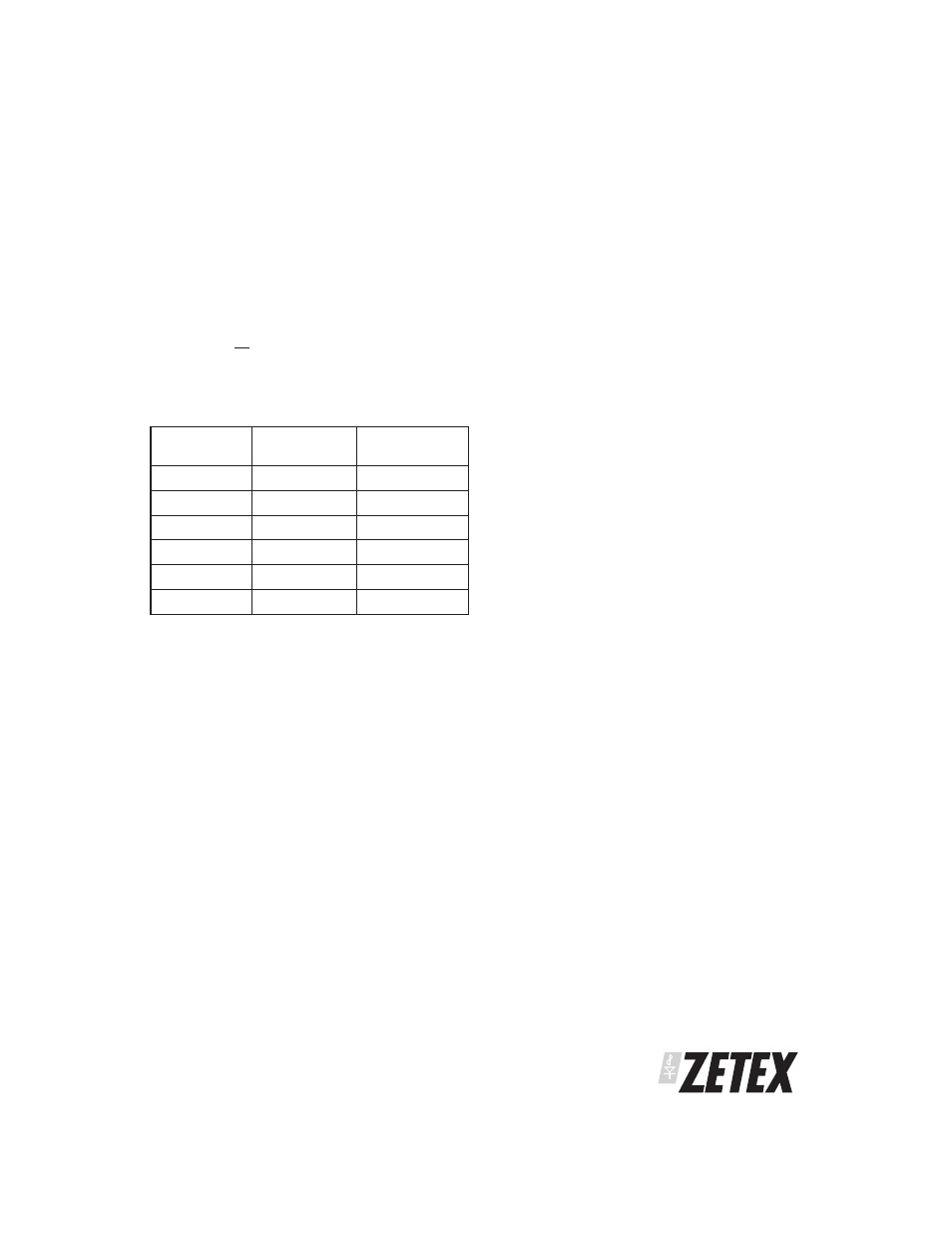

The following table gives suggested values for

various output voltages.

Output voltage can be adjusted from V

IN

+ V

F

to the

maximum output voltage rating of the internal

switch, 30V.

Once the nominal output voltage has been set, it can

be adjusted to a lower value by applying a pulse

width modulated (PWM) control signal to the EN pin.

PWM adjustment permits the device to be turned on

and the output voltage set by a single logic signal

applied to the EN pin. No external resistors are

required and the amplitude of the control signal is

not critical, providing it conforms to the limits

defined in the electrical characteristics.

1) PWM output voltage adjustment (analogue mode)

During this mode of operation the device operation is

continuous, providing a low ripple output voltage

(V

OUT

) directly proportional to the duty cycle (D) of

the logic signal applied to the EN pin according to the

relationship:

V

OUT

= D x V

OUT(nom)

Square wave signals applied to the EN pin, for

example, will turn the device on and produce a

nominal regulated output of 13.5V.

The ZXLD1615 contains a timing circuit that switches

the device on a few microseconds after the

application of a rising edge to EN and turns it back

off again nominally 120

µs after the falling edge of

EN. For continuous PWM mode operation, the

frequency of the control signal must therefore be

maintained above 10kHz at all times, to prevent the

internal delay circuit from timing out and switching

the device into standby mode. The maximum

frequency applied to EN should be limited to 100kHz

to minimize errors due to internal switching delays

2) PWM output voltage adjustment (gated mode)

This method of adjustment can be used in

applications where the output ripple is less important

than the supply current. The method of adjustment is

the same as in 1) above, however, during this mode

of operation, the device is gated on and off,

providing an average output voltage (V

OUT

) directly

proportional to the duty cycle (D) of the logic signal

applied to the EN pin according to the relationship:

V

OUT(AVG)

= D x V

OUT(nom)

The ripple on this voltage will be determined by the

size of the output capacitor.

The output voltage can be adjusted all the way down

to the input voltage by either method of PWM

control, but for best results, the duty cycle range

should be kept within the specified range. Lower duty

cycles will result in increased output ripple and

non-linearity in the relationship between duty cycle

and output voltage. If a greater control range is

required, the nominal output can be reduced by the

use of external resistors before the PWM signal is

applied.

Minimizing output voltage ripple

For applications requiring lower output ripple it may

be necessary to add a small ceramic capacitor in

parallel with R2. A value of 4.7pF is suitable for most

output ranges.

ZXLD1615

S E M I C O N D U C T O R S

ISSUE 3 - AUGUST 2004

7

Required

output voltage

R1

R2

5V

270K

⍀

1M

⍀

12V

91K

⍀

1M

⍀

18V

60K

⍀

1M

⍀

21V

51K

⍀

1M

⍀

25V

43K

⍀

1M

⍀

28V

39K

⍀

1M

⍀