Diodes ZVNL110G User Manual

Zvnl110g

SOT223 N-CHANNEL ENHANCEMENT MODE

LOW THRESHOLD VERTICAL DMOS FET

ISSUE 2 - FEBRUARY 1996

✪

FEATURES

*

LOW R

DS(ON)

- 3

Ω

PARTMARKING DETAIL - ZVNL110

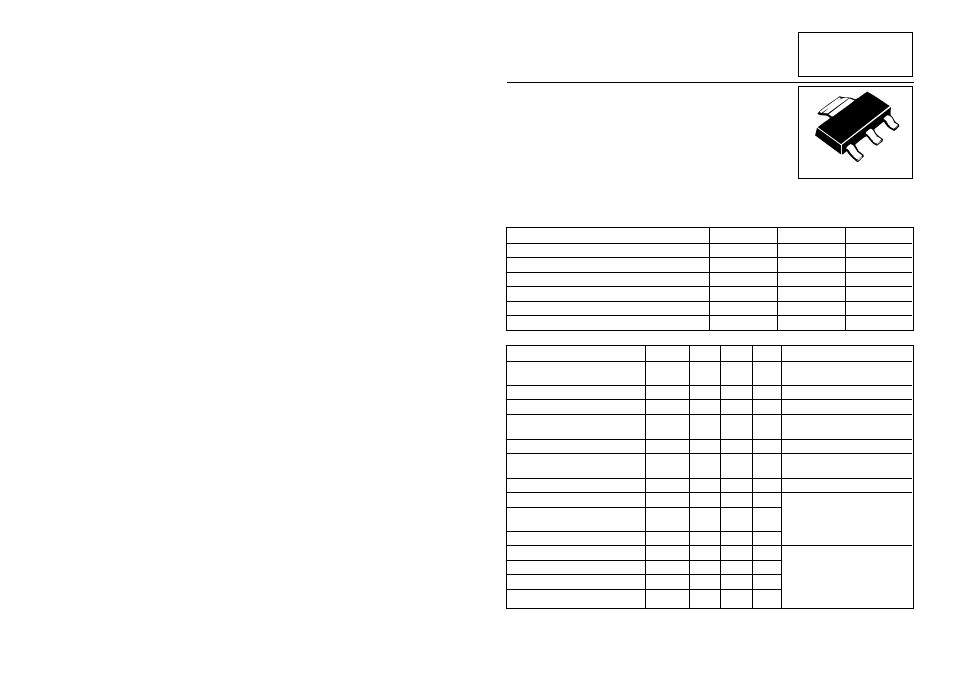

ABSOLUTE MAXIMUM RATINGS.

PARAMETER

SYMBOL

VALUE

UNIT

Drain-Source Voltage

V

DS

100

V

Continuous Drain Current at T

amb

=25°C

I

D

600

mA

Pulsed Drain Current

I

DM

6

A

Gate-Source Voltage

V

GS

±

20

V

Power Dissipation at T

amb

=25°C

P

tot

2

W

Operating and Storage Temperature Range

T

j

:T

stg

-55 to +150

°C

ELECTRICAL CHARACTERISTICS (at T

amb

= 25°C unless otherwise stated).

PARAMETER

SYMBOL MIN.

MAX.

UNIT CONDITIONS.

Drain-Source Breakdown

Voltage

BV

DSS

100

V

I

D

=1mA, V

GS

=0V

Gate-Source Threshold Voltage V

GS(th)

0.75

1.5

V

I

D

=1mA, V

DS

= V

GS

Gate-Body Leakage

I

GSS

100

nA

V

GS

=

±

20V, V

DS

=0V

Zero Gate Voltage Drain

Current

I

DSS

10

100

µ

A

µ

A

V

DS

=100V, V

GS

=0V

V

DS

=80V, V

GS

=0V, T=125°C

(2)

On-State Drain Current(1)

I

D(on)

750

mA

V

DS

=25V, V

GS

=5V

Static Drain-Source On-State

Resistance (1)

R

DS(on)

4.5

3.0

Ω

Ω

V

GS

=5V, I

D

=250mA

V

GS

=10V, I

D

=500mA

Forward Transconductance(1)(2) g

fs

225

mS

V

DS

=25V, I

D

=500mA

Input Capacitance (2)

C

iss

75

pF

Common Source Output

Capacitance (2)

C

oss

25

pF

V

DS

=25V, V

GS

=0V, f=1MHz

Reverse Transfer Capacitance (2) C

rss

8

pF

Turn-On Delay Time (2)(3)

t

d(on)

7

ns

V

DD

≈

25V, I

D

=1A, V

GS

=10V

Rise Time (2)(3)

t

r

12

ns

Turn-Off Delay Time (2)(3)

t

d(off)

15

ns

Fall Time (2)(3)

t

f

13

ns

(1) Measured under pulsed conditions. Width=300

µ

s. Duty cycle

≤

2% (2) Sample test.

(3) Switching times measured with 50

Ω

source impedance and <5ns rise time on a pulse generator

ZVNL110G

3 - 419

D

D

S

G