5 chipset, North bridge chipset configuration, Execute disable bit [enabled – Asus P5B Deluxe/WiFi-AP User Manual

Page 92: Hyper threading technology [enabled, Inter(r) speedstep (tm) tech. [disabled, Configuration options: [disabled] [automatic

-

Chapter 4: BIOS setup

Select Screen

Select Item

Enter Go to Sub Screen

F1 General Help

F10 Save and Exit

ESC Exit

v02.58 (C)Copyright 1985-2006, American Megatrends, Inc.

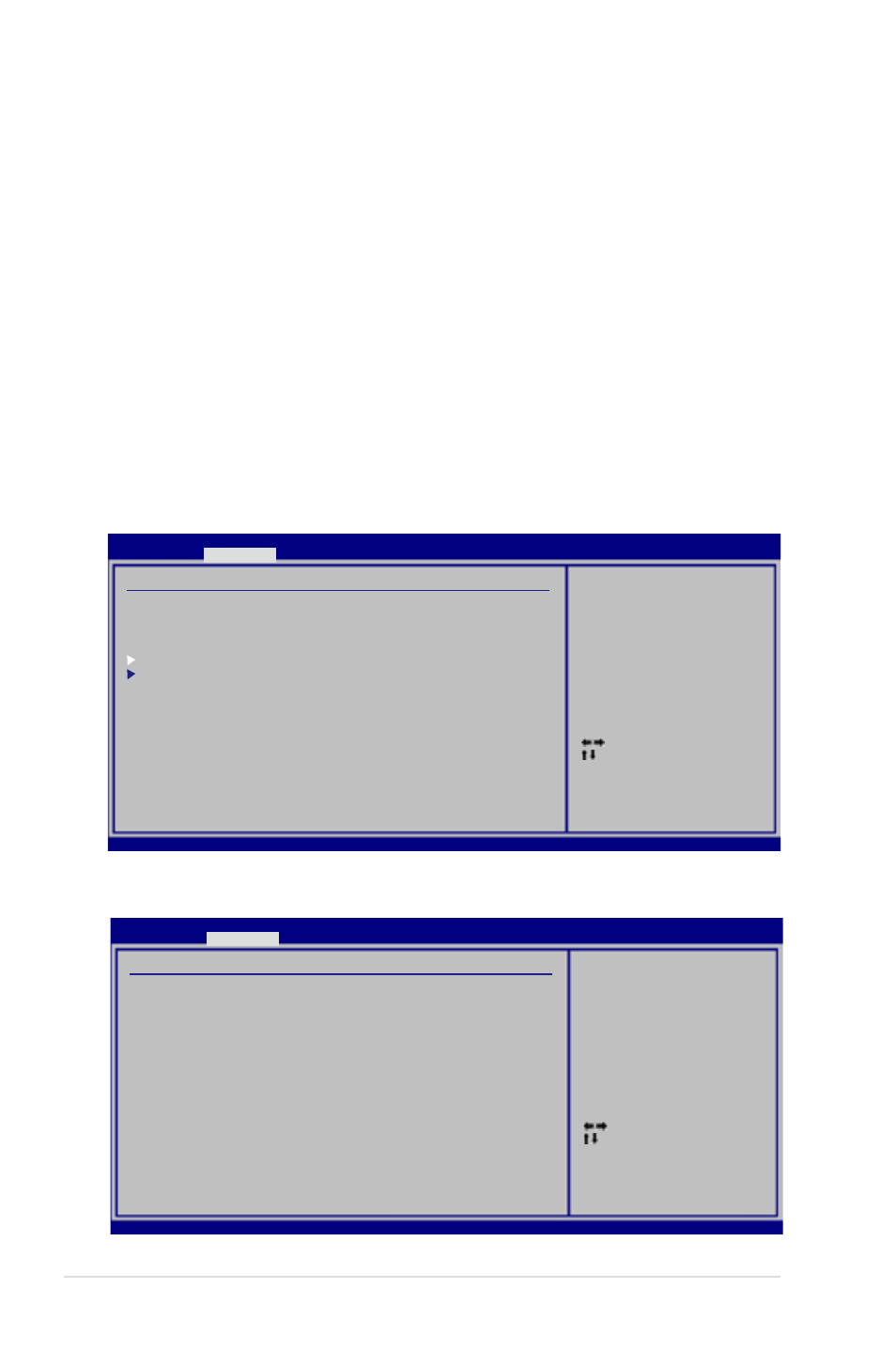

BIOS SETUP UTILITY

Advanced

4.4.5

Chipset

The Chipset menu allows you to change the advanced chipset settings. Select an

item then press

Advanced Chipset Settings

WARMING: Setting wrong values in below sections

may cause system to malfunction.

North Bridge Configuration

South Bridge Configuration

Configure North Bridge

features.

Select Screen

Select Item

+- Change Option

F1 General Help

F10 Save and Exit

ESC Exit

v02.58 (C)Copyright 1985-2006, American Megatrends, Inc.

BIOS SETUP UTILITY

Advanced

North Bridge Chipset Configuration

Memory Remap Feature

[Disabled]

Configure DRAM Timing by SPD

[Enabled]

Initiate Graphic Adapter

[PEG/PCI]

PEG Port Configuration

PEG Force x1

[Disabled]

PEG Link Mode

[Auto]

North Bridge Chipset Configuration

ENABLED: Allow

remapping of

overlapped PCI memory

above the total

physical memory.

DISABLED: Do not allow

remapping of memory

Execute Disable Bit [Enabled]

Allows you to enable or disable the No-Execution Page Protection Technology.

Setting this item to [Disabled] forces the XD feature flag to always return to zero

(0). Configuration options: [Disabled] [Enabled]

Hyper Threading Technology [Enabled]

Allows you to enable or disable the Hyper Threading Technology.

Configuration options: [Enabled] [Disabled]

Inter(R) SpeedStep (tm) Tech. [Disabled]

Configuration options: [Disabled] [Automatic]