Applications information, Reset (rs) and clear ( clr ), Unipolar output – Rainbow Electronics MAX5173 User Manual

Page 12: Bipolar output

MAX5171/MAX5173

Low-Power, Serial, 14-Bit DACs

with Force/Sense Voltage Output

12

______________________________________________________________________________________

microcontroller I/O pins required. During power-down,

this output will retain its digital state prior to shutdown.

When CLR is pulled low, UPO will reset to its program-

med default state. See Table 1 for specific commands

to control the UPO.

Reset (RS) and Clear (

CLR)

The MAX5171/MAX5173 offers a clear pin which resets

the output voltage. If RST = DGND, then CLR resets the

output voltage to the minimum voltage (0 if no offset is

introduced). If RST = V

DD

, then CLR resets the output

voltage to midscale. In either case, CLR resets UPO to

its programmed default state.

___________Applications Information

Unipolar Output

Figure 6 shows the MAX5171/MAX5173 configured for

unipolar, rail-to-rail operation with a gain of +2V/V. Table 2

lists the codes for unipolar output voltages. The output

voltage is limited to V

DD

.

Bipolar Output

Figure 7 shows the MAX5171/MAX5173 configured for

bipolar output operation. The output voltage is given by

the following equation (FB = OUT):

where N represents the numeric value of the DAC’s

binary input code and VREF is the voltage of the exter-

nal reference. Table 3 shows digital codes and the cor-

responding output voltage for Figure 7’s circuit.

V

V

N

OUT

REF

=

−

⋅

2

16384

1

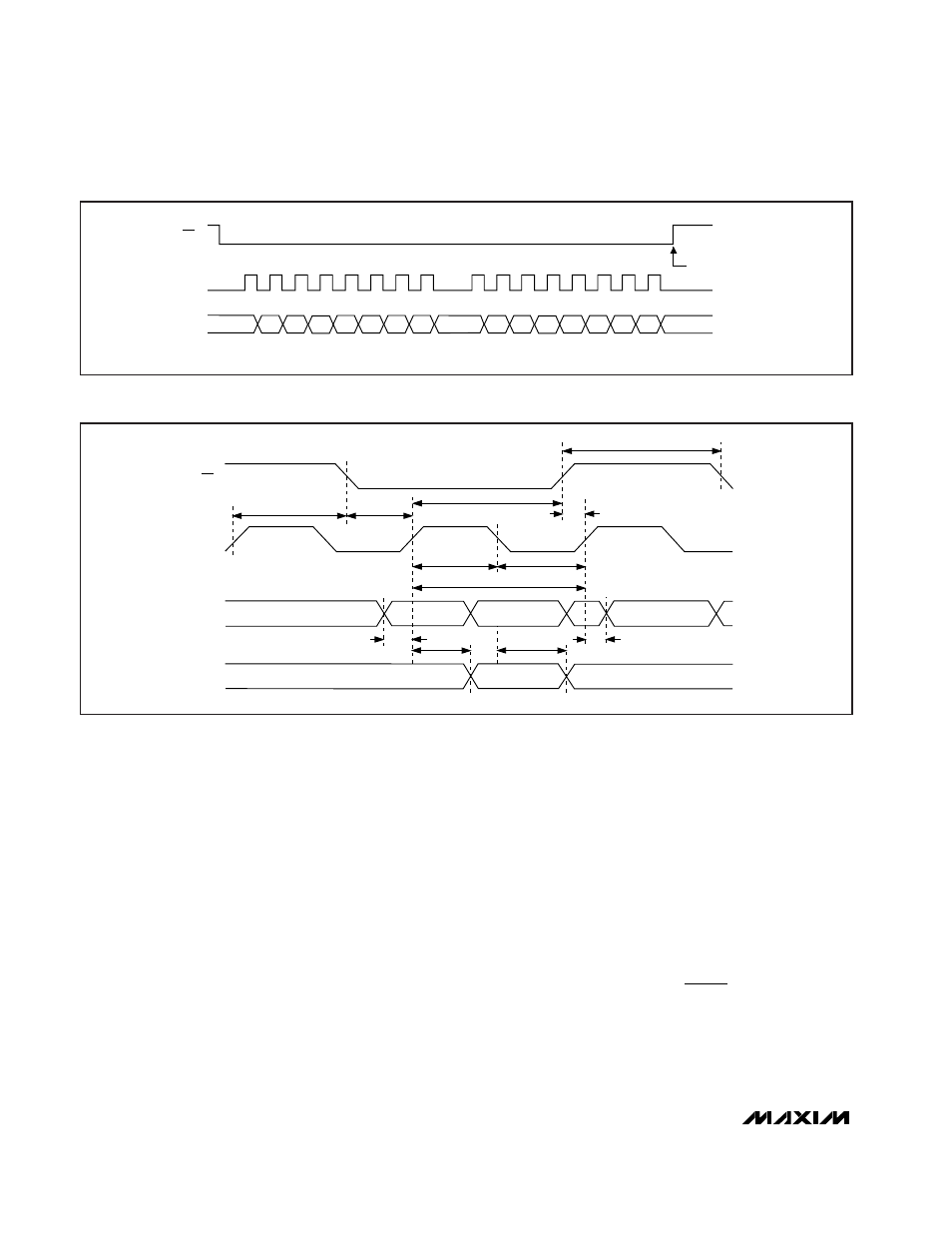

CS

SCLK

DIN

COMMAND

EXECUTED

9

8

16

1

C1

C2

S0

C0

D9

D8

D7

D6

D3

D2

D1

D0

S2

S1

D5

D4

Figure 4. Serial-Interface Timing Diagram

CS

SCLK

DIN

DOUT

t

CSW

t

CS1

t

CSH

t

CSS

t

CSO

t

D02

t

CH

t

CL

t

CP

t

D01

t

DS

t

DH

Figure 5. Detailed Serial-Interface Timing Diagram