Electrical characteristics (continued) – Rainbow Electronics MAX1669 User Manual

Page 3

MAX1669

Fan Controller and Remote Temperature Sensor

with SMBus Serial Interface

_______________________________________________________________________________________

3

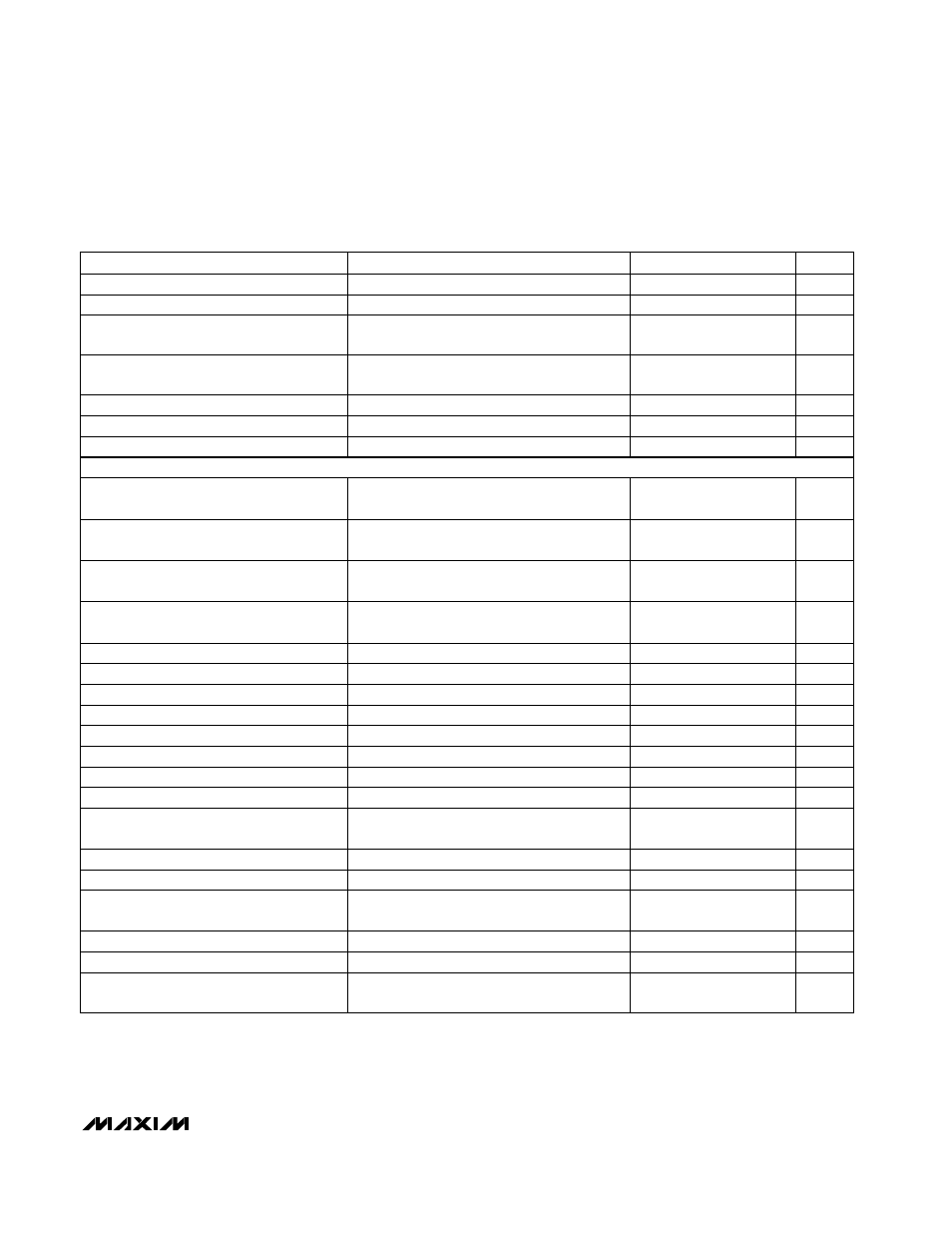

ELECTRICAL CHARACTERISTICS (continued)

(V

CC

= +3.3V, T

A

= 0°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

Logic Input High Voltage

PARAMETER

MIN

TYP

MAX

UNITS

FAN PWM Frequency Error

-20

+20

%

FAN Total Unadjusted Error

-4

4

%FS

FAN Output Voltage High

2.96

3.06

V

CONDITIONS

PWM mode, any setting

DAC mode, any setting, R

L

= 10k

Ω to GND

DAC mode, FAN duty factor = 1111b,

I

OUT

= 5mA

SYNC Input Low Period

500

ns

SYNC Input High Period

500

ns

SYNC Capture Range

140

260

400

kHz

2.1

V

Logic Input Low Voltage

0.8

V

SMBDATA, ALERT, OVERT, I/O1, I/O2

Output Low Sink Current

6

mA

FAN Output Voltage Low

0.05

0.2

V

ALERT, OVERT, I/O1, I/O2 Output

High Leakage Current

1

µA

Logic Input Current

-1

1

µA

SMBus Input Capacitance

5

pF

SMBus Clock Frequency

DC

100

kHz

SMBCLK Clock Low Time (t

LOW

)

4.7

µs

SMBCLK Clock High Time (t

HIGH

)

4

µs

SMBus Rise Time

1

µs

SMBus Fall Time

300

ns

SMBus Start Condition Setup Time

4.7

µs

SMBus Repeated Start Condition Setup

Time (t

SU:STA

)

500

ns

SMBus Start Condition Hold Time (t

HD:STA

)

4

µs

SMBus Stop Condition Setup Time (t

SU:STO

)

4

µs

SMBus Data Valid to SMBCLK

Rising-Edge Time (t

SU:DAT

)

250

ns

Pin forced to 5.5V

Logic inputs forced to V

CC

or GND

ADD_, I/O1, I/O2, SYNC, SMBCLK, SMBDATA;

V

CC

= 3V to 5.5V

ADD_, I/O1, I/O2, SYNC, SMBCLK, SMBDATA;

V

CC

= 3V to 5.5V

SMBCLK, SMBDATA

(Note 3)

Pin forced to 0.4V

10% to 10% points

90% to 90% points

SMBCLK, SMBDATA, 10% to 90% points

SMBCLK, SMBDATA, 90% to 10% points

90% to 90% points

DAC mode, FAN duty factor = 0000b,

I

OUT

= -5mA

10% of SMBDATA to 90% of SMBCLK

90% of SMBCLK to 10% of SMBDATA

10% or 90% of SMBDATA to 10% of SMBCLK

SMBus Data-Hold Time (

t

HD:DAT

)

0

µs

SMBus Bus-Free Time (t

BUF

)

4.7

µs

SMBCLK Falling Edge to SMBus

Data-Valid Time

1

µs

(Note 4)

Between start/stop conditions

Master clocking-in data

SMBus INTERFACE (Figures 7, 8)