7 interrupt status register 2-address 42h, 8 interrupt mask register 1-address 43h, 9 interrupt mask register 2-address 44h – Rainbow Electronics LM87 User Manual

Page 27: 10 reserved register -address 45h, 11 ci clear register-address 46h, 12 vid0-3/fan divisor register-address 47h, Functional description

Functional Description

(Continued)

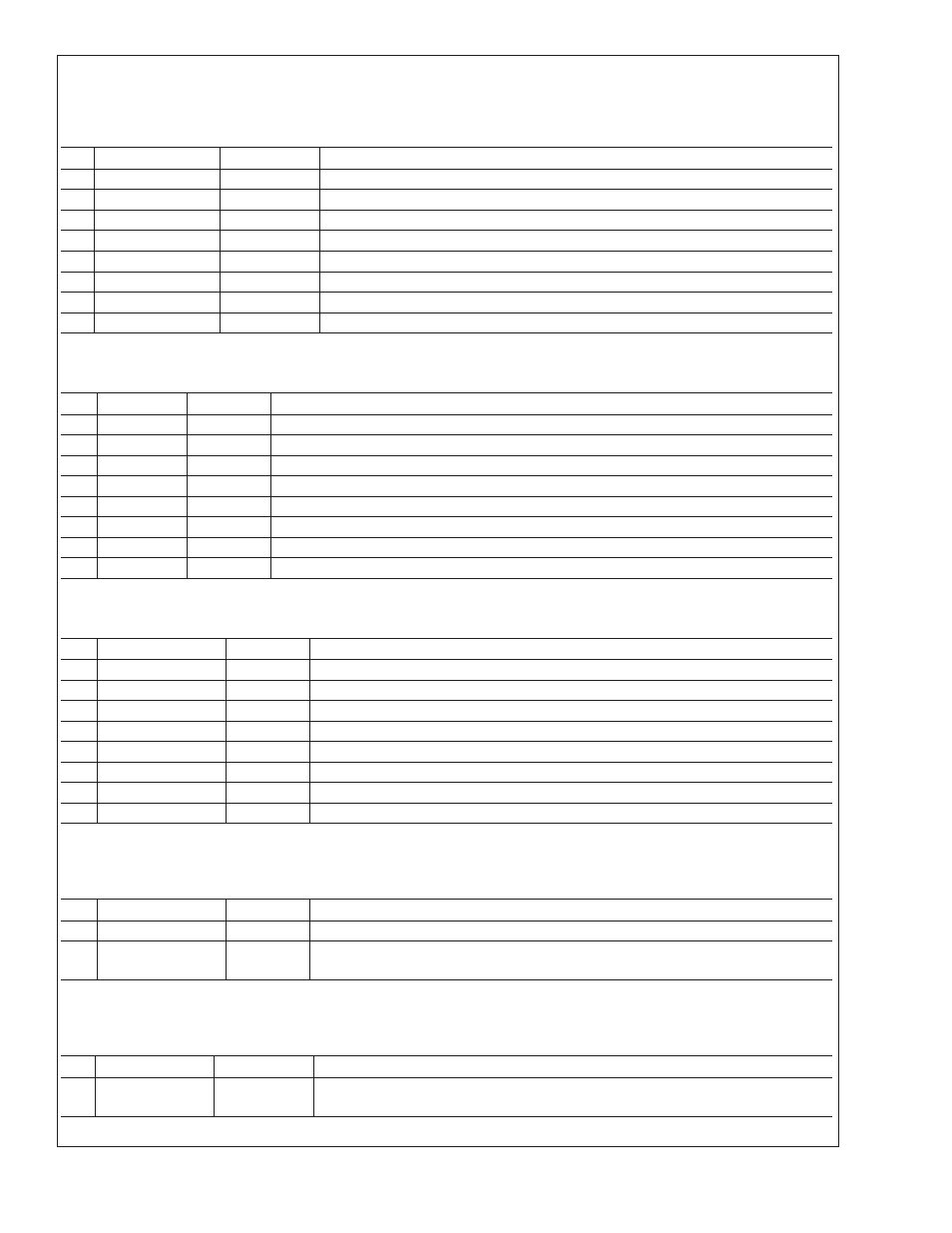

13.7 Interrupt Status Register 2 — Address 42h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/Write

Description

0

+12Vin

Read Only

A one indicates a High or Low limit has been exceeded.

1

Vccp2

Read Only

A one indicates a High or Low limit has been exceeded.

2

Reserved

Read Only

3

Reserved

Read Only

4

CI

Read Only

A one indicates the CI (Chassis Intrusion) input has gone high.

5

THERM#

Read Only

A one indicates the THERM# input has been pulled low by external circuitry.

6

D1 Fault

Read Only

A one indicates the D1 inputs are shorted to Vcc or open circuit.

7

D2 Fault

Read Only

A one indicates the D2 inputs are shorted to Vcc or open circuit.

13.8 Interrupt Mask Register 1 — Address 43h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/Write

Description

0

+2.5Vin/D2+

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

1

Vccp1

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

2

Vcc

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

3

+5Vin

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

4

Int. Temp.

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

5

Ext. Temp.

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

6

FAN1/AIN1

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

7

FAN2/AIN2

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

13.9 Interrupt Mask Register 2 — Address 44h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/Write

Description

0

+12Vin

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

1

Vccp2

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

2

Reserved

Read/Write

3

Reserved

Read/Write

4

Chassis Intrusion

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

5

THERM#

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

6

D1 Fault

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

7

D2 Fault

Read/Write

A one disables the corresponding interrupt status bit for INT# interrupt.

13.10 Reserved Register — Address 45h

Power on default –

<

7:0

>

= 00h. Read/Write for backwards

compatibility.

13.11 CI Clear Register — Address 46h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/Write

Description

0-6

Reserved

Read/Write

7

CI Clear

Read/Write

A one outputs a minimum 20 ms (minimum) active low pulse on the Chassis Intrusion

pin. The register bit self clears after the pulse has been output.

13.12 VID0-3/Fan Divisor Register — Address 47h

Power on default –

<

7:4

>

is 0101, and

<

3:0

>

is mapped to

VID

<

3:0

>

Bit

Name

Read/Write

Description

0-3

VID

<

3:0

>

Read Only

The VID

<

3:0

>

inputs from the Pentium/PRO power supplies that indicate the

operating voltage (e.g. 1.5 V to 2.9 V).

LM87

www.national.com

27