Serial interface, Programming the beamformer – Rainbow Electronics MAX2038 User Manual

Page 20

MAX2038

Ultrasound VGA Integrated

with CW Octal Mixer

20

______________________________________________________________________________________

Serial Interface

The serial interface of the MAX2038 programs the LO for

16, 8, or 4 quadrature phases using a serial shift regis-

ter implementation. Data is shifted into the device on

DIN. The serial shift register clock is applied to the CLK

input. The serial shift register has 5 bits per channel.

The first 4 bits are for phase programming, and the fifth

bit enables or disables each channel of the mixer array.

Each mixer can be programmed to 1 of 16 phases;

therefore, 4 bits are required for each channel for pro-

gramming. The master high-frequency mixer clock is

applied to differential inputs LO_LVDS+ and LO_LVDS-

(for modes 1 and 2) and LO_ (for modes 3 and 4). The

LOAD input is provided to allow the user to load the

phase counters with the programming values to gener-

ate the correct LO phases. The input signals for mixing

are applied to the eight differential inputs, CWIN_+ and

CWIN_-. The summed I/Q baseband differential outputs

are provided on CW_IOUT+/- and CW_QOUT+/-.

CW_M1 and CW_M2 are used to select one of the four

possible modes of operation. See Table 1.

The serial interface is designed to allow multiple

devices to be easily daisy chained in order to minimize

program interface wiring. DOUT is available for this

daisy-chain function.

Programming the Beamformer

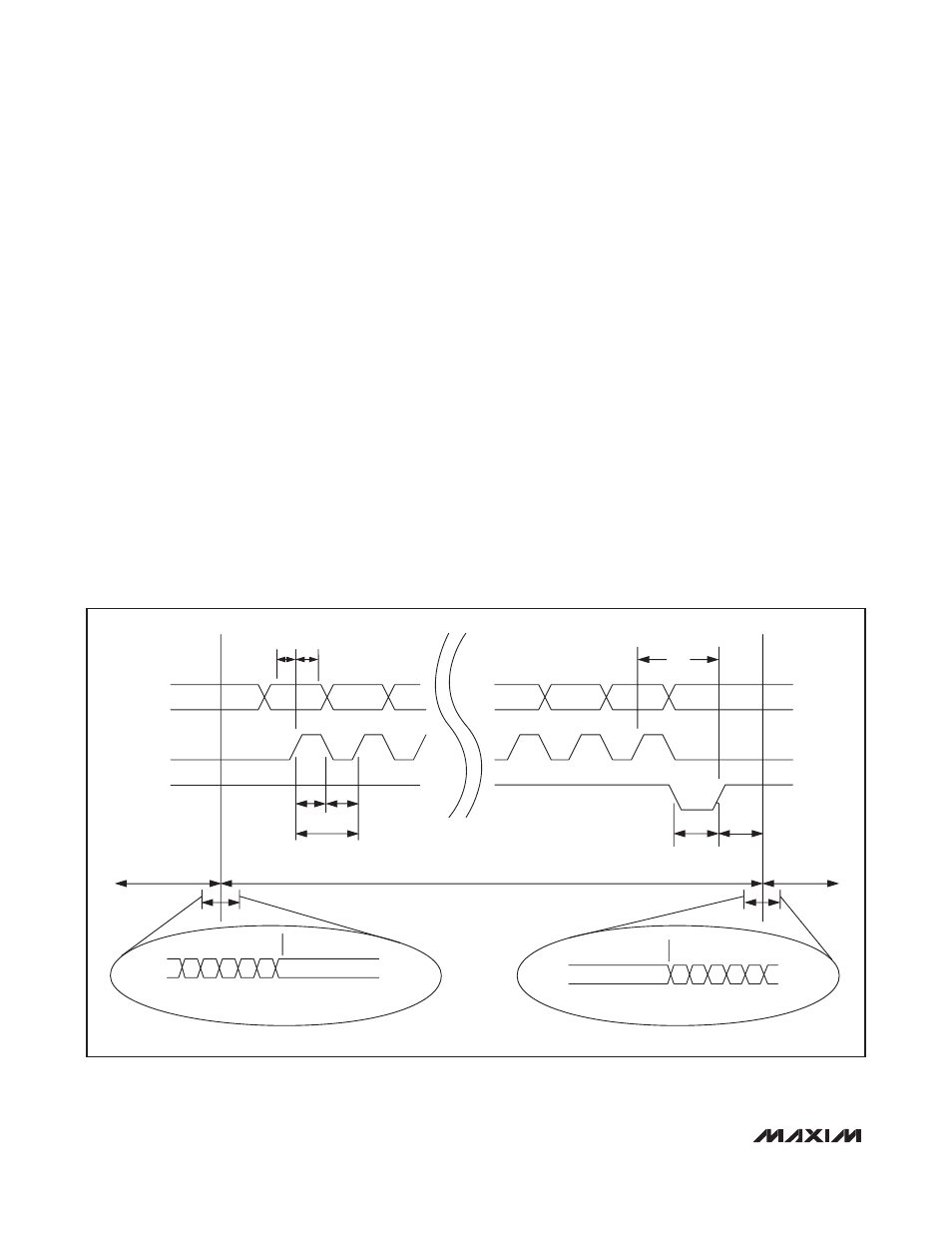

During normal CWD operation, the mixer clock at LO_ or

LO_LVDS+/- is on and the programming signals on DIN,

CLK, and LOAD are off. (LOAD = high, CLK = low, and

DIN = don’t care, but fixed to a high or low). To start the

programming sequence, turn off the mixer clock. Data is

shifted into the shift register at a recommended 10MHz

programming rate or 100ns minimum data clock

period/time. See Figure 5 for timing details.

After the shift registers are programmed, pull the LOAD

bus to logic-low and then back to logic-high to load the

internal counters into I/Q phase divider/selectors with

the proper values. LOAD must remain low for a mini-

mum time of t

CLH

. The user turns on the mixer clock to

start beamforming. The clock must turn on such that it

starts at the beginning of a mixer clock cycle.

DIN

CLK

LOAD

t

DCLKPWH

t

DCLKPWL

t

LD

t

CLH

t

DCLK

t

DSU

t

HLD

t

LDMIXCLK

MIXER

CLOCK ON

MIXER

CLOCK ON

MIXER

CLOCK OFF

MIXER

CLOCK ON

MIXER

CLOCK OFF

MIXER

CLOCK OFF

MIXER

CLOCK ON

Figure 5. Shift Register Timing Diagram