Electrical characteristics (continued) – Rainbow Electronics MAX1418 User Manual

Page 4

MAX1418

15-Bit, 65Msps ADC with -78.2dBFS

Noise Floor for IF Applications

4

_______________________________________________________________________________________

Note 1: Dynamic performance is based on a 32,768-point data record with a sampling frequency of f

SAMPLE

= 65.0117120MHz, an

input frequency of f

IN

= f

SAMPLE

x (35283/32768) = 70.001472MHz, and a frequency bin size of 1984Hz. Close-in (f

IN

±23.8kHz) and low-frequency (DC to 47.6kHz) bins are excluded from the spectrum analysis.

Note 2: Apply the same voltage levels to DV

CC

and DRV

CC

Note 3: Guaranteed by design and characterization.

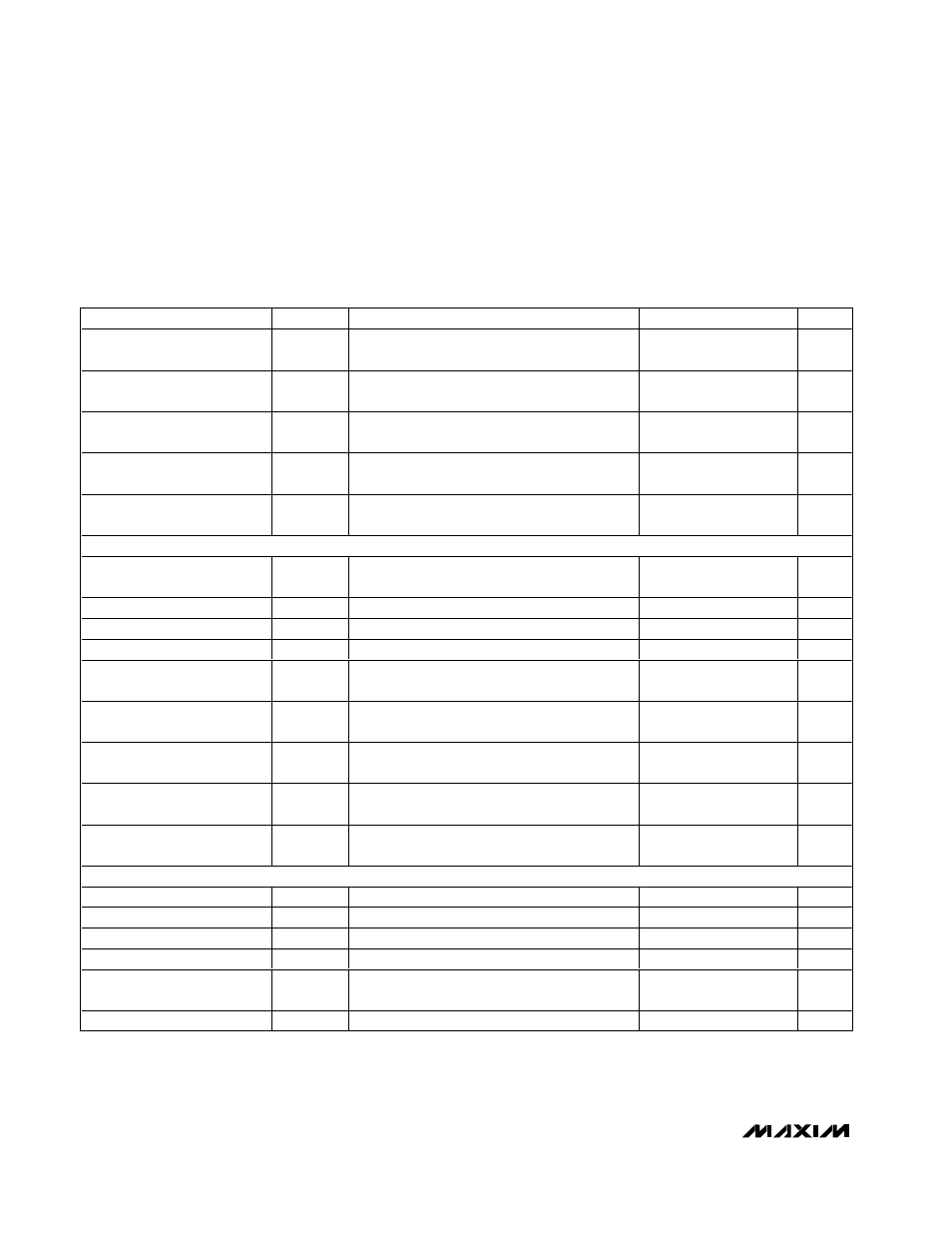

ELECTRICAL CHARACTERISTICS (continued)

(AV

CC

= 5V, DV

CC

= DRV

CC

= 2.5V, GND = 0, INP and INN driven differentially with -2dBFS, CLKP and CLKN driven differentially

with a 2V

P-P

sinusoidal input signal, C

L

= 5pF at digital outputs, f

CLK

= 65MHz, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical

values are at T

A

= +25°C, unless otherwise noted. ≥+25°C guaranteed by production test, <+25°C guaranteed by design and char-

acterization.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Pipeline Latency

t

LATENCY

3

Clock

cycles

CLKP Rising Edge to DATA

Not Valid

t

DNV

(Note 3)

2.6

3.8

5.7

ns

CLKP Rising Edge to DATA

Valid (Guaranteed)

t

DGV

(Note 3)

3.4

5.2

8.6

ns

DATA Setup Time

(Before DAV Rising Edge)

t

SETUP

(Note 3)

t

CLKP

-

0.5

t

CLKP

+ 1.3

t

CLKP

+ 2.4

ns

DATA Hold Time

(After DAV Rising Edge)

t

HOLD

(Note 3)

t

CLKN

-

3.6

t

CLKN

-

2.8

t

CLKN

-

2.0

ns

TIMING CHARACTERISTICS (DV

CC

= DRV

CC

= 3.3V)

Figure

4

CLKP/CLKN Duty Cycle

Duty cycle

50

±5

%

Effective Aperture Delay

t

AD

230

ps

Output Data Delay

t

DAT

(Note 3)

2.8

4.1

6.5

ns

Data Valid Delay

t

DAV

(Note 3)

5.3

6.3

8.6

ns

Pipeline Latency

t

LATENCY

3

Clock

cycles

CLKP Rising Edge to

DATA Not Valid

t

DNV

(Note 3)

2.5

3.4

5.2

ns

CLKP Rising Edge to

DATA Valid (Guaranteed)

t

DGV

(Note 3)

3.2

4.4

7.4

ns

DATA Setup Time

(Before DAV Rising Edge)

t

SETUP

(Note 3)

t

CLKP

+ 0.2

t

CLKP

+ 1.7

t

CLKP

+ 2.8

ns

DATA Hold Time

(After DAV Rising Edge)

t

HOLD

(Note 3)

t

CLKN

-

3.5

t

CLKN

-

2.7

t

CLKN

-

2.0

ns

POWER REQUIREMENTS

Analog Supply Voltage Range

AV

CC

5 ±3%

V

Digital Supply Voltage Range

DV

CC

(Note 2)

2.5 to 3.5

V

Output Supply Voltage Range

DRV

CC

(Note 2)

2.5 to 3.5

V

Analog Supply Current

I

AVCC

382

447

mA

D i g i tal + Outp ut S up p l y C ur r ent

I

DVCC

+

DRV

CC

f

CLK

= 65MHz, C

LOAD

= 5pF

35.5

42

mA

Analog Power Dissipation

PDISS

2000

mW