Design procedure – Rainbow Electronics MAX1638 User Manual

Page 11

MAX1638

High-Speed Step-Down Controller with

Synchronous Rectification for CPU Power

______________________________________________________________________________________

11

High-Side Current Sensing

The common-mode input range of the current-sense

inputs (CSH and CSL) extends to V

CC

, so it is possible

to configure the circuit with the current-sense resistor

on the input side rather than on the load side (Figure 5).

This configuration improves efficiency by reducing the

power dissipation in the sense resistor according to the

duty ratio.

In the high-side configuration, if the output is shorted

directly to GND through a low-resistance path, the cur-

rent-sense comparator may be unable to enforce a cur-

rent limit. Under such conditions, circuit parasitics such

as MOSFET R

DS(ON)

typically limit the short-circuit cur-

rent to a value around the peak-current-limit setting.

Attach a lowpass-filter network between the current-

sense pins and resistor to reduce high-frequency com-

mon-mode noise. The filter should be designed with a

time constant of around one-fifth of the on-time (130ns

at 600kHz, for example). Resistors in the 20

Ω

to 100

Ω

range are recommended for R7 and R8. Connect the

filter capacitors C11 and C12 from V

CC

to CSH and

CSL, respectively.

Values of 39

Ω

and 3.3nF are suitable for many designs.

Place the current-sense filter network close to the IC,

within 0.1 in (2.5mm) of the CSH and CSL pins.

Overvoltage Protection

When the output exceeds the set voltage, the synchro-

nous rectifier (N2) is driven high (and N1 is driven low).

This causes the inductor to quickly dissipate any stored

energy and force the fault current to flow to ground.

Current is limited by the source impedance and para-

sitic resistance of the current path, so a fuse is required

in series with the +5V input to protect against low-

impedance faults, such as a shorted high-side MOS-

FET. Otherwise, the low-side MOSFET will eventually

fail. DL will go low if the input voltage drops below the

undervoltage lockout point.

Internal Soft-Start

Soft-start allows a gradual increase of the internal cur-

rent limit at start-up to reduce input surge currents. An

internal DAC raises the current-limit threshold from 0V

to 100mV in four steps (25mV, 50mV, 75mV, and

100mV) over the span of 1536 oscillator cycles.

__________________Design Procedure

Setting the Output Voltage

Select the output voltage using the D0–D4 pins. The

MAX1638 uses an internal 5-bit DAC as a feedback-

resistor voltage divider. The output voltage can be digi-

tally set from 1.3V to 3.5V using the D0–D4 inputs

(Table 2).

D0–D4 are logic inputs and accept both TTL and

CMOS voltage levels. The MAX1638 has both FB and

AGND inputs, allowing a Kelvin connection for remote

voltage and ground sensing to eliminate the effects of

trace resistance on the feedback voltage. (See

PC

Board Layout Considerations

for further details.) FB

input current is 0.1µA (max).

The MAX1638 DAC codes (D0–D4) were designed for

compatibility with the Intel VRM 8.2 specification for

output voltages between 1.8V (code 00101) and 3.5V

(code 10000). Codes 00110 to 01111 have also been

designed for 50mV increments, allowing set voltages

down to 1.300V. Code 11111 turns off the buck controller,

placing the IC in a shutdown mode (0.2mA typical).

Choosing the

Error-Amplifier Gain

Set the error-amplifier gain to match the voltage-preci-

sion requirements of the CPU used. The MAX1638’s

loop-gain control input (LG) allows trade-offs in DC/AC

voltage accuracy versus output filter capacitor require-

ments. AC load regulation can be set to 0.5%, 1%,

or 2% by connecting LG as shown in Table 3.

DC load regulation is typically 10 times better than AC

load regulation, and is determined by the gain set by

the LG pin.

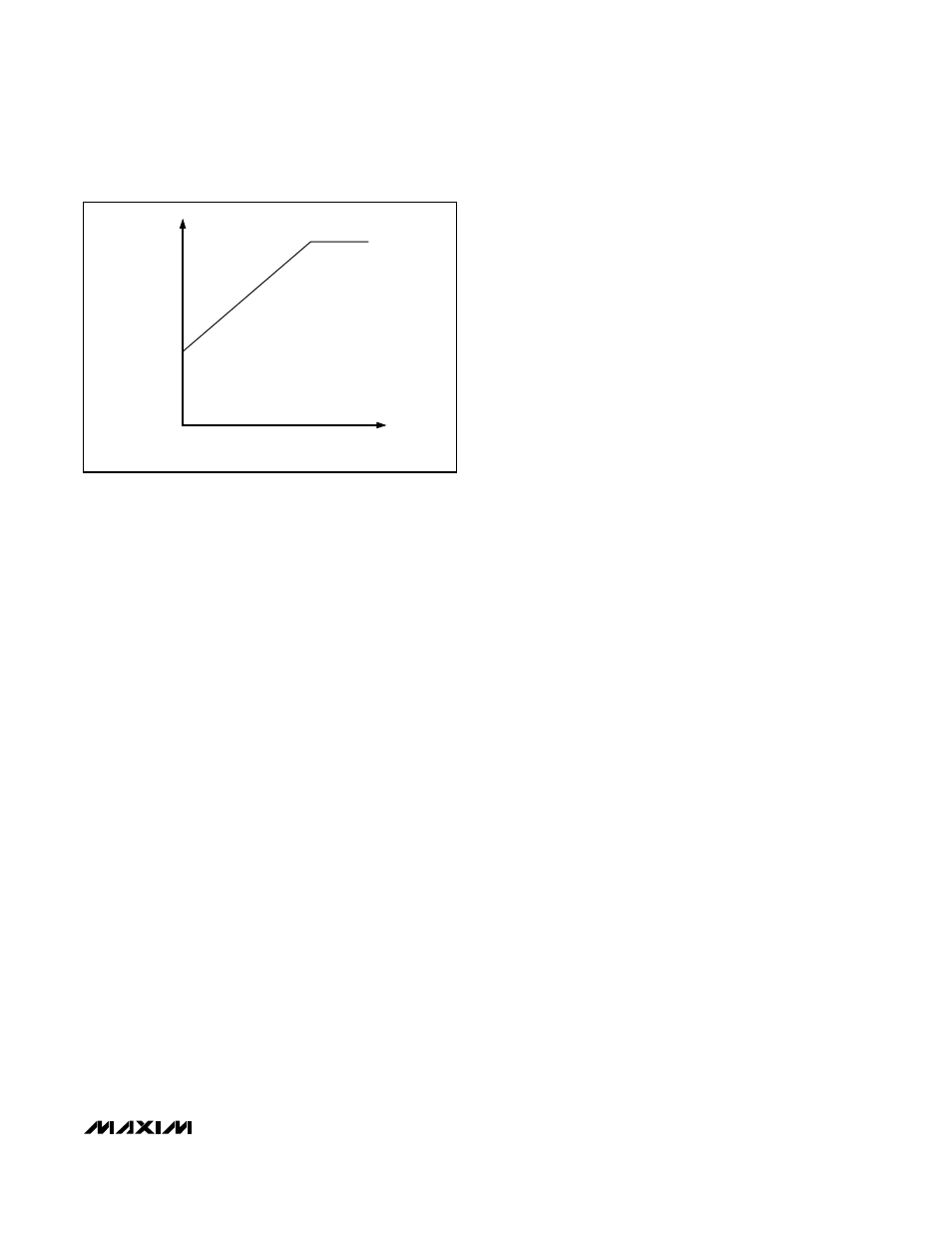

0

20

10

50

40

30

60

70

100

90

80

20 30

10

0

40 50 60 70 80 90 100

V

FB

(%)

I

LIM

(%)

Figure 4. Foldback Current Limit