Detailed description, Applications information – Rainbow Electronics MAX100 User Manual

Page 11

MAX100

250Msps, 8-Bit ADC with Track/Hold

______________________________________________________________________________________

11

_______________Detailed Description

Converter Operation

The parallel or “flash” architecture used by the MAX100

provides the fastest multibit conversion of all common

integrated ADC designs. The basic element of a flash

(as with all other ADC architectures) is the comparator,

which has a positive input, a negative input, and an

output. If the voltage at the positive input is higher than

the negative input (connected to a reference), the out-

put will be high. If the positive input voltage is lower

than the reference, the output will be low. A typical n-

bit flash consists of 2

n

-1 comparators with negative

inputs evenly spaced at 1LSB increments from the bot-

tom to the top of the reference ladder. For n = 8, there

will be 255 comparators.

For any input voltage, all the comparators with negative

inputs connected to the reference ladder below the

input voltage will have outputs of 1, and all compara-

tors with negative inputs above the input voltage will

have outputs of 0. Decode logic is provided to convert

this information into a parallel n-bit digital word (the out-

put) corresponding to the number of LSBs (minus 1)

that the input voltage is above the level set at the bot-

tom of the ladder.

Finally, the comparators contain latch circuitry and are

clocked. This allows the comparators to function as

described above when, for example, clock is low.

When clock goes high (samples) the comparator will

latch and hold its state until the clock goes low again.

Track/Hold

As with all ADCs, if the input waveform is changing

rapidly during the conversion the effective bits and

SNR will decrease. The MAX100 has an internal

track/hold (T/H) that increases attainable effective-bits

performance and allows more accurate capture of ana-

log data at high conversion rates.

The internal T/H circuit provides two important circuit

functions for the MAX100:

1) Its nominal voltage gain of 4 reduces the input dri-

ving signal to ±270mV differential (assuming a

±1.02V reference).

2) It provides a differential 50

Ω

input that allows easy

interface to the MAX100.

Data Flow

The MAX100 contains an internal T/H amplifier that

stores the analog input voltage for the ADC to convert.

The differential inputs AIN+ and AIN- are tracked con-

tinuously between data samples. When a negative CLK

edge is applied, the T/H enters hold mode (Figure 5).

When CLK goes low, the most recent sample is pre-

sented to the ADC’s input comparators. Internal pro-

cessing of the sampled data is delayed for several

clock cycles before it is available at outputs AData or

BData. All output data is timed with respect to DCLK

and DCLK (Figures 1–4).

__________Applications Information

Analog Input Ranges

Although the normal operating range is ±270mV, the

MAX100 can be operated with up to ±500mV on each

input with respect to ground. This extended input level

includes the analog signal and any DC common-mode

voltage.

To obtain a full-scale digital output with differential input

drive, a nominal +270mV must be applied between

AIN+ and AIN-. That is, AIN+ = +135mV and AIN- =

-135mV (with no DC offset). Mid-scale digital output

code occurs when there is no voltage difference across

the analog inputs. Zero-scale digital output code, with

differential -270mV drive, occurs when AIN+ = -135mV

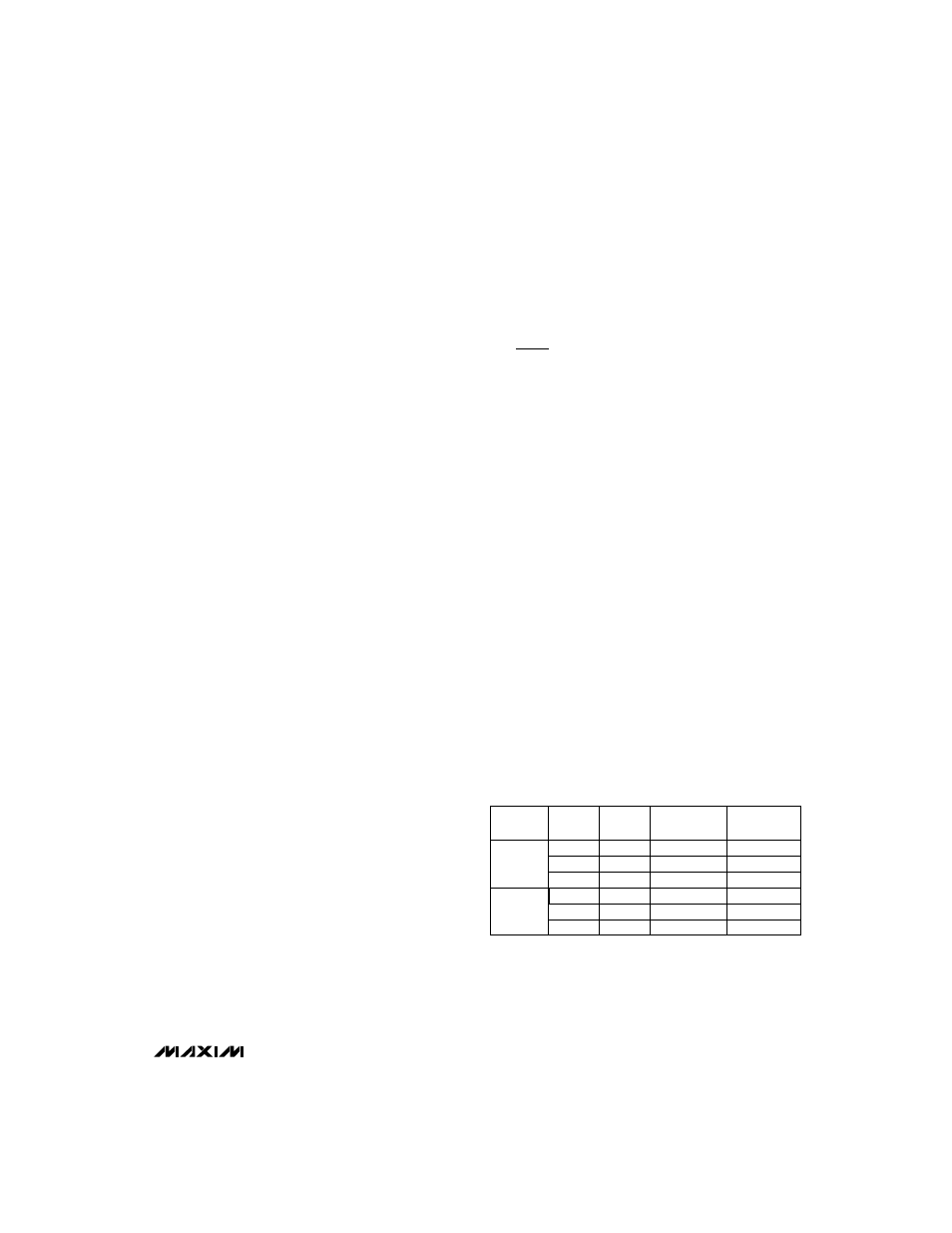

and AIN- = +135mV. Table 2 shows how the output of

the converter stays at all ones (full scale) when over

ranged or all zeros (zero scale) when under ranged.

For single-ended operation:

1) Apply a DC offset to one of the analog inputs, or

leave one input open. (Both AIN+ and AIN- are ter-

minated internally with 50

Ω

to analog ground.)

2) Drive the other input with a ±270mV + offset to

obtain either full- or zero-scale digital output. If a DC

common-mode offset is used, the total voltage swing

allowed is ±500mV (analog signal plus offset with

respect to ground).

Table 1. Input Voltage Range

**An offset V

IO

, as specified in the DC electrical parameters, may

be present at the input. Compensate for this offset by either

adjusting the reference voltage (VA

RT

or VA

RB

), or introducing an

offset voltage in one of the input terminals AIN + or AIN-.

+135

-135

0

0

AIN+**

(mV)

AIN-**

(mV)

INPUT

11111111

10000000

OUTPUT

CODE

full scale

mid scale

MSB to LSB

-135

+135

+270

0

00000000

11111111

zero scale

full scale

0

0

-270

0

10000000

00000000

mid scale

zero scale

Single

Ended

Differential