Note 1), Note 3), Note 4) – Rainbow Electronics ADC1175 User Manual

Page 7: Note 5), Note 6), Note 9), Note 10), Converter electrical characteristics, Adc1 175

Converter Electrical Characteristics

(Continued)

The following specifications apply for AV

DD

= DV

DD

= +5.0V

DC

, OE = 0V, V

RT

= +2.6V, V

RB

= 0.6V, C

L

= 20 pF,

f

CLK

= 20MHz at 50% duty cycle. Boldface limits apply for T

A

= T

MIN

to T

MAX

; all other limits T

A

= 25˚C (Notes 7, 8)

Symbol

Parameter

Conditions

Typical

Limits

Units

SINAD

Signal-to- Noise & Distortion

f

IN

= 1.31 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, V

IN

= FS - 2 LSB

f

IN

= 9.9 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, f

CLK

= 30 MHz

47

46

45

40

43

dB(min)

SNR

Signal-to- Noise Ratio

f

IN

= 1.31 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, V

IN

= FS - 2 LSB

f

IN

= 9.9 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, f

CLK

= 30 MHz

47

47

42

45

44

dB(min)

SFDR

Spurious Free Dynamic Range

f

IN

= 1.31 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, V

IN

= FS - 2 LSB

f

IN

= 9.9 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, f

CLK

= 30 MHz

56

58

53

46

dB

THD

Total Harmonic Distortion

f

IN

= 1.31 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, V

IN

= FS - 2 LSB

f

IN

= 9.9 MHz, V

IN

= FS - 2 LSB

f

IN

= 4.43 MHz, f

CLK

= 30 MHz

−55

−57

−52

−47

dB

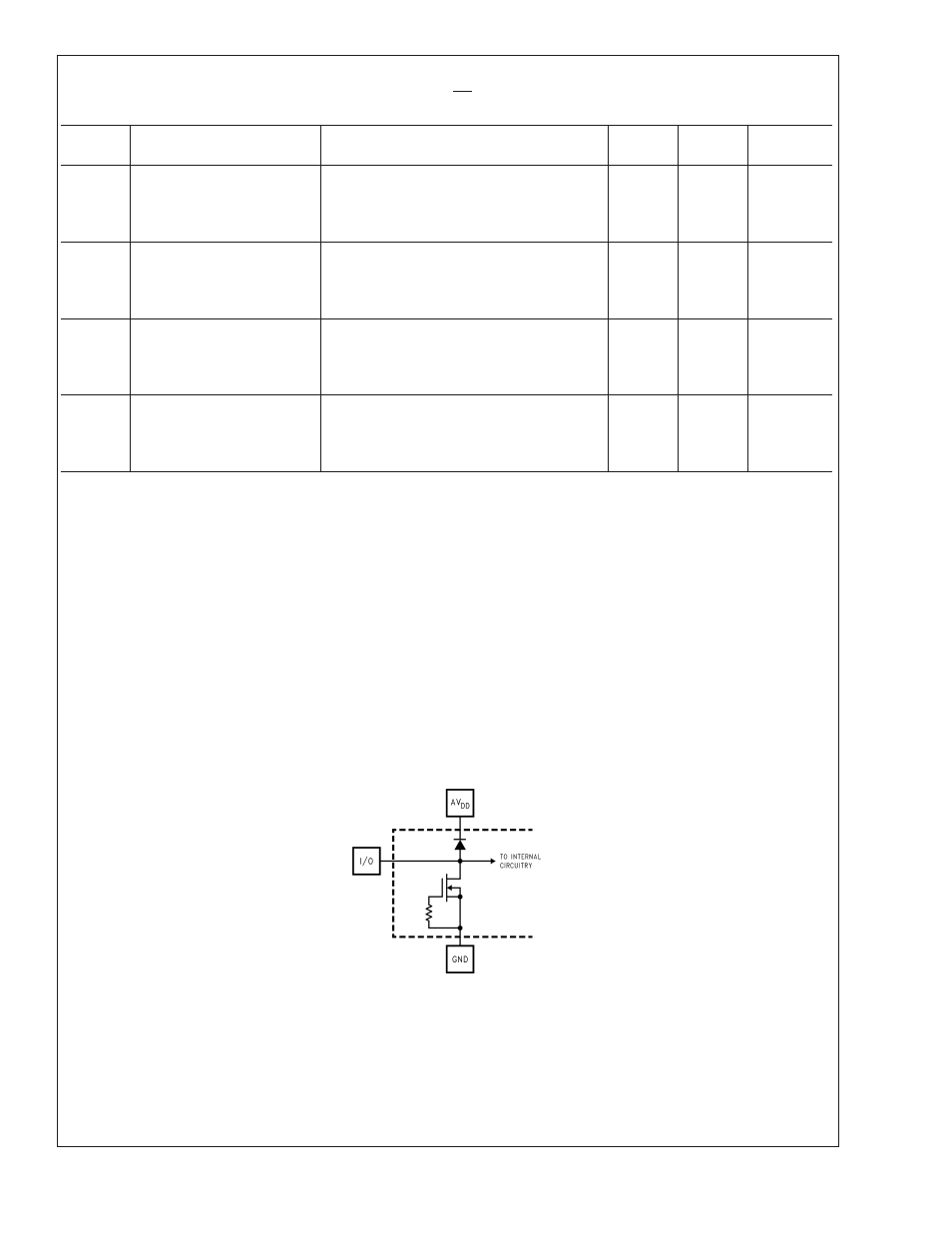

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test

conditions.

Note 2: All voltages are measured with respect to GND = AV

SS

= DV

SS

= 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds the power supplies (that is, less than AV

SS

or DV

SS

, or greater than AV

DD

or DV

DD

), the current at that pin should

be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of

25 mA to two.

Note 4: The absolute maximum junction temperatures (T

J

max) for this device is 150˚C. The maximum allowable power dissipation is dictated by T

J

max, the

junction-to-ambient thermal resistance

θ

JA

, and the ambient temperature, T

A

, and can be calculated using the formula P

D

MAX = (T

J

max - T

A

)/

θ

JA

. In the 24-pin

TSSOP,

θ

JA

is 92˚C/W, so P

D

MAX = 1,358 mW at 25˚C and 815 mW at the maximum operating ambient temperature of 75˚C. (Typical thermal resistance,

θ

JA

, of

this part is 98˚C/W for the EIAJ SOIC). Note that the power dissipation of this device under normal operation will typically be about 101 mW (60 mW quiescent power

+ 33 mW reference ladder power + 8 mW due to 1 TTL loan on each digital output. The values for maximum power dissipation listed above will be reached only when

the ADC1175 is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is

reversed). Obviously, such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5k

Ω resistor. Machine model is 220 pf discharged through ZERO Ω.

Note 6: See AN450, "Surface Mounting Methods and Their Effect on Product Reliability", or the section entitled "Surface Mount" found in any post 1986 National

Semiconductor Linear Data Book, for other methods of soldering surface mount devices.

Note 7: The analog inputs are protected as shown below. Input voltage magnitudes up to 6.5V or to 500 mV below GND will not damage this device. However, errors

in the A/D conversion can occur if the input goes above V

DD

or below GND by more than 50 mV. As an example, if AV

DD

is 4.75V

DC

, the full-scale input voltage must

be

≤4.80V

DC

to ensure accurate conversions.

10009210

Note 8: To guarantee accuracy, it is required that AV

DD

and DV

DD

be well bypassed. Each supply pin must be decoupled with separate bypass capacitors.

Note 9: Typical figures are at T

J

= 25˚C, and represent most likely parametric norms. Test limits are guaranteed to National’s AOQL (Average Outgoing Quality

Level).

Note 10: At least two clock cycles must be presented to the ADC1175 after power up. See Section 4.0 for details.

ADC1

175

www.national.com

7