Clock operations-reading the clock – Rainbow Electronics DS1642 User Manual

Page 2

DS1642

2 of 11

prevents time loss as the timekeeping countdown continues unabated by access to time register data. The

DS1642 also contains its own power-fail circuitry which deselects the device when the V

CC

supply is in

an out-of-tolerance condition. This feature prevents loss of data from unpredictable system operation

brought on by low V

CC

as errant access and update cycles are avoided.

CLOCK OPERATIONS-READING THE CLOCK

While the double-buffered register structure reduces the chance of reading incorrect data, internal updates

to the DS1642 clock registers should be halted before clock data is read to prevent reading of data in

transition. However, halting the internal clock register updating process does not affect clock accuracy.

Updating is halted when a 1 is written into the read bit, the 7th most significant bit in the control register.

As long as a 1 remains in that position, updating is halted. After a halt is issued, the registers reflect the

count, that is day, date, and time that was current at the moment the halt command was issued. However,

the internal clock registers of the double-buffered system continue to update so that the clock accuracy is

not affected by the access of data. All of the DS1642 registers are updated simultaneously after the clock

status is reset. Updating is within a second after the read bit is written to 0.

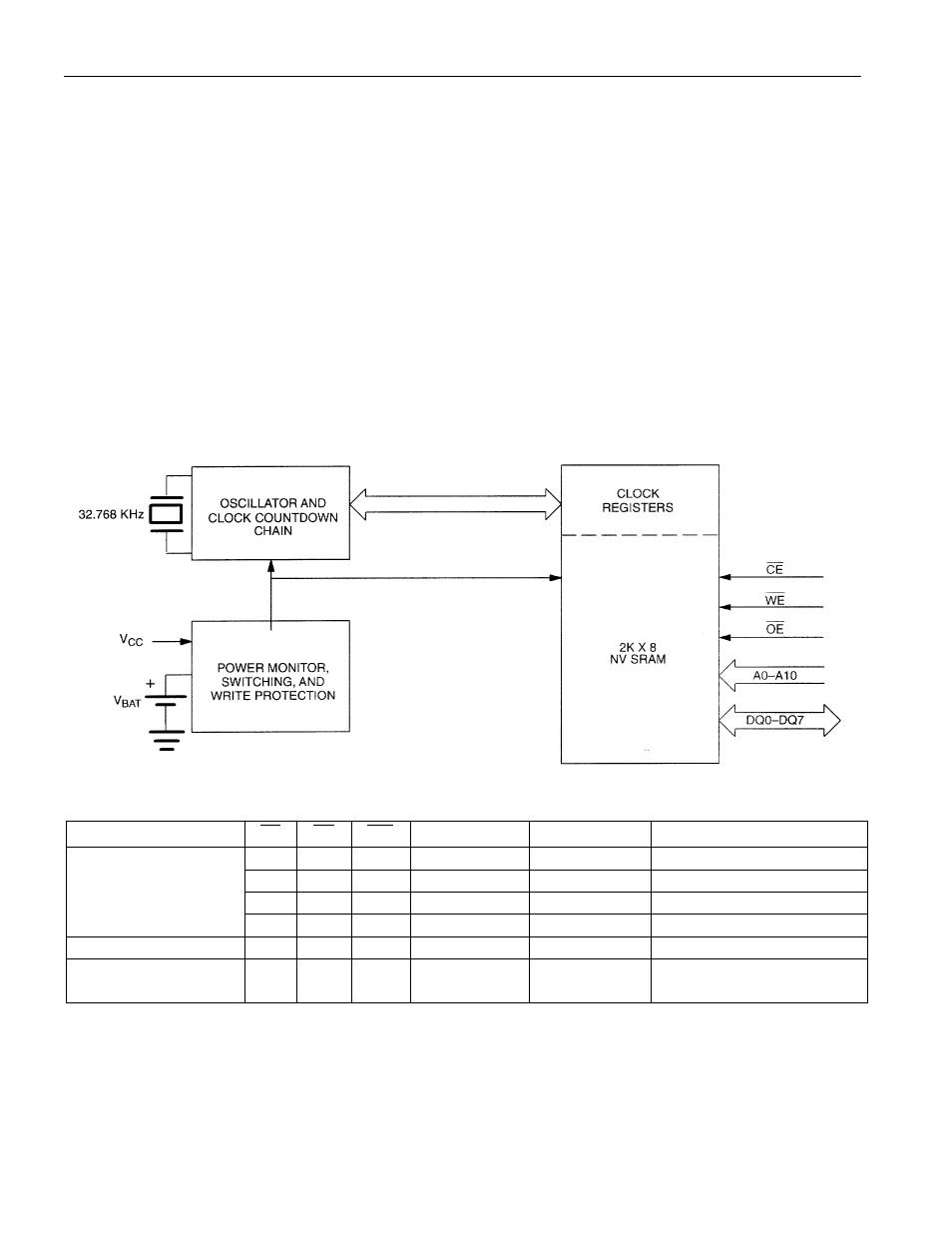

DS1642 BLOCK DIAGRAM Figure 1

DS1642 TRUTH TABLE Table 1

V

CC

CE

OE

WE

MODE

DQ

POWER

V

IH

X

X

DESELECT

HIGH Z

STANDBY

V

IL

X

V

IL

WRITE

DATA IN

ACTIVE

V

IL

V

IL

V

IH

READ

DATA OUT

ACTIVE

5 VOLTS ± 10%

V

IL

V

IH

V

IH

READ

HIGH Z

ACTIVE

<4.5 VOLTS >V

BAT

X

X

X

DESELECT

HIGH Z

CMOS STANDBY

BAT X X X DESELECT HIGH Z DATA RETENTION MODE