Rainbow Electronics DS1670 User Manual

Page 6

DS1670

6 of 17

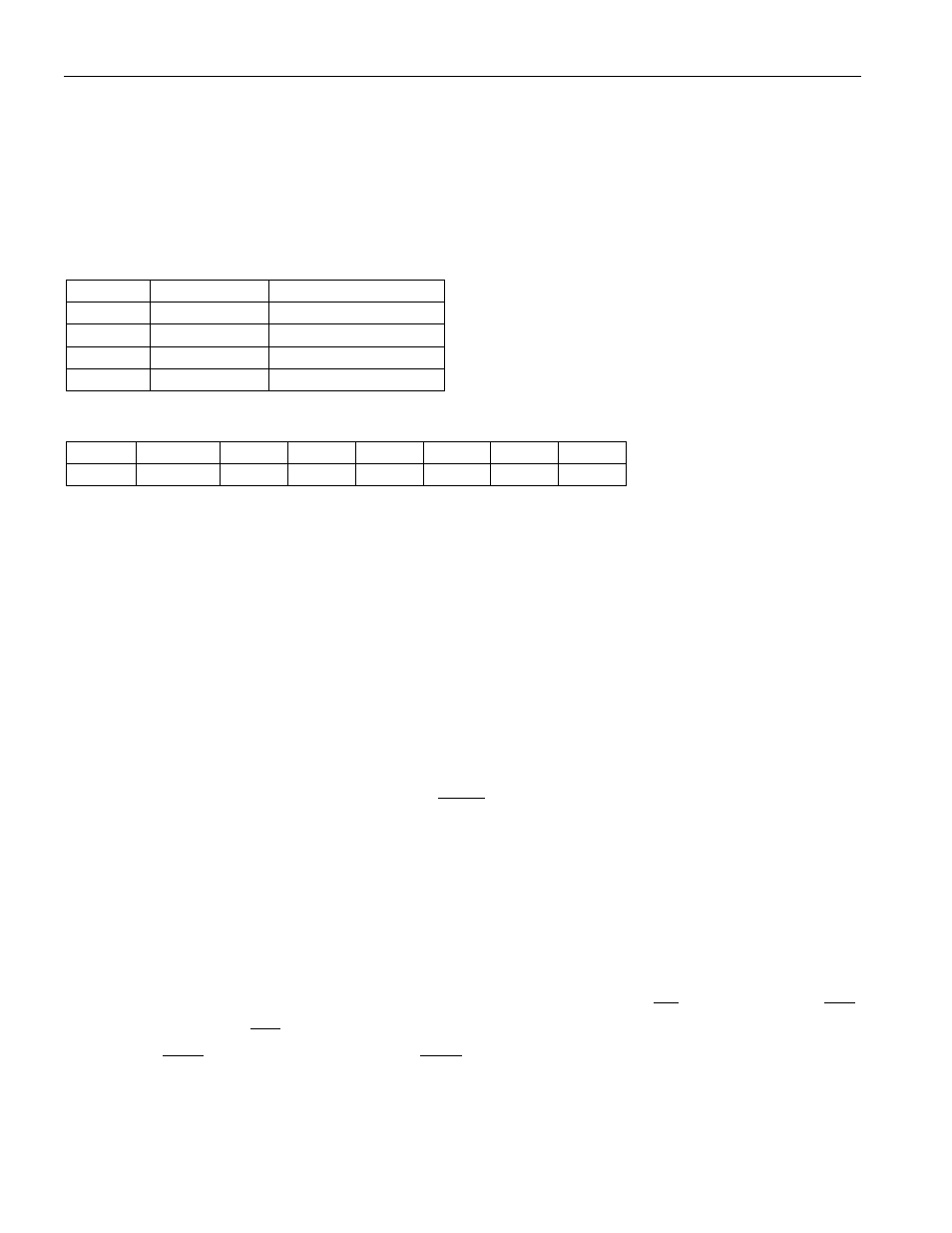

AIS0-AIS1 (Analog Input Select) - These 2 bits are used to determine the analog input for the analog-to-

digital conversion. Table 2 lists the specific analog input that is selected by these two bits.

AIE (Alarm Interrupt Enable) - When set to a logic 1, this bit permits the Interrupt Request Flag

(IRQF) bit in the status register to assert INT. When the AIE bit is set to logic 0, the IRQF bit does not

initiate the INT signal.

ANALOG INPUT SELECTION Table 2

AIS1

AIS0

ANALOG INPUT

0

0

NONE

0

1

AIN0

1

0

AIN1

1

1

AIN2

STATUS REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

CU

LOBAT

0

0

0

0

0

IRQF

CU (Conversion Update In Progress) - When this bit is a 1, an update to the ADC Register (register

0Eh) will occur within 488 ms. When this bit is a 0, an update to the ADC Register will not occur for at

least 244 ms.

LOBAT (Low Battery Flag) - This bit reflects the status of the backup power source connected to the

V BAT pin. When V

BAT

is greater than 2.5 volts, LOBAT is set to a logic 0. When V

BAT

is less than 2.3

volts, LOBAT is set to a logic 1.

IRQF (Interrupt Request Flag) - A logic 1 in the Interrupt Request Flag bit indicates that the current

time has matched the time of day Alarm registers. If the AIE bit is also a logic 1, the INT pin will go

high. IRQF is cleared by reading or writing to any of the alarm registers.

POWER-UP DEFAULT STATES

These bits are set to a one upon initial power-up:

EOSC , TD1 and TD0. These bits are cleared upon

initial power-up: WP, AIS1, and AIS0.

NONVOLATILE SRAM CONTROLLER

The DS1670 provides automatic backup and write protection for external SRAM. This function is

provided by gating the chip enable signals and by providing a constant power supply through the V

CCO

pin. The DS1670 was specifically designed with the Intel 80186 and 386EX microprocessors in mind.

As such, the DS1670 has the capability to provide access to the external SRAM in either byte-wide or

word-wide format. This capability is provided by the chip enable scheme. Three input signals and two

output signals are used for enabling the external SRAM(s) (see Figure 4).

CEI

(chip enable in),

BHE

(byte high enable), and

BLE

(byte low enable) are used for enabling either one or two external SRAMs

through the

CEOL

(chip enable low) and the

CEOH

(chip enable high) outputs. Table 3 illustrates the

function of these pins.