Microprocessor monitor, Watchdog register – 0dh, Watchdog time-out bits table 2 – Rainbow Electronics DS1680 User Manual

Page 10

DS1680

10 of 23

MICROPROCESSOR MONITOR

The DS1680 monitors three vital conditions for a microprocessor: power supply, software execution, and

external override.

First, a precision temperature-compensated reference and comparator circuit monitors the status of V

CC

.

When an out-of-tolerance condition occurs, an internal power-fail signal is generated that forces the

RST

pin to the active state, thus warning a processor-based system of impending power failure. When V

CC

returns to an in- tolerance condition upon power-up, the reset signal is kept in the active state for t

RST

to

allow the power supply and microprocessor to stabilize. Note, however, that if the

EOSC

bit is set to a

logic 1 (to disable the oscillator during battery-backup mode), the

RST

signal will be kept in an active

state for t

RST

plus the start-up time of the oscillator.

The second monitoring function is pushbutton reset control. The DS1680 provides for a pushbutton

switch to be connected to the

RST

output pin. When the DS1680 is not in a reset cycle, it continuously

monitors the

RST

signal for a low-going edge. If an edge is detected, the DS1680 will debounce the

switch by pulling the

RST

line low. After the internal timer has expired, the DS1680 will continue to

monitor the

RST

line. If the line is still low, the DS1680 will continue to monitor the line looking for a

rising edge. Upon detecting release, the DS1680 will force the

RST

line low and hold it low for t

RST

.

The third microprocessor monitoring function provided by the DS1680 is a watchdog timer. The

watchdog timer function forces

RST

to the active state when the

ST

input is not stimulated within the

predetermined time period. The time period is set by the time delay (TD) bits in the watchdog register.

The time delay can be set to 250ms, 500ms, or 1000ms. If TD0 and TD1 are both set to zero, the

watchdog timer is disabled. When enabled, the watchdog timer starts timing out from the set time period

as soon as

RST

is inactive. The default setting is for the watchdog timer to be enabled with 1000ms time

delay. If a high-to- low transition occurs on the

ST

input pin prior to time-out, the watchdog timer is reset

and begins to time-out again. If the watchdog timer is allowed to time-out, the

RST

signal is driven to the

active state for t

RST

. The

ST

input can be derived from microprocessor address signals, data signals,

and/or control signals. To guarantee that the watchdog timer does not time-out, a high-to- low transition

must occur at or less than the minimum period.

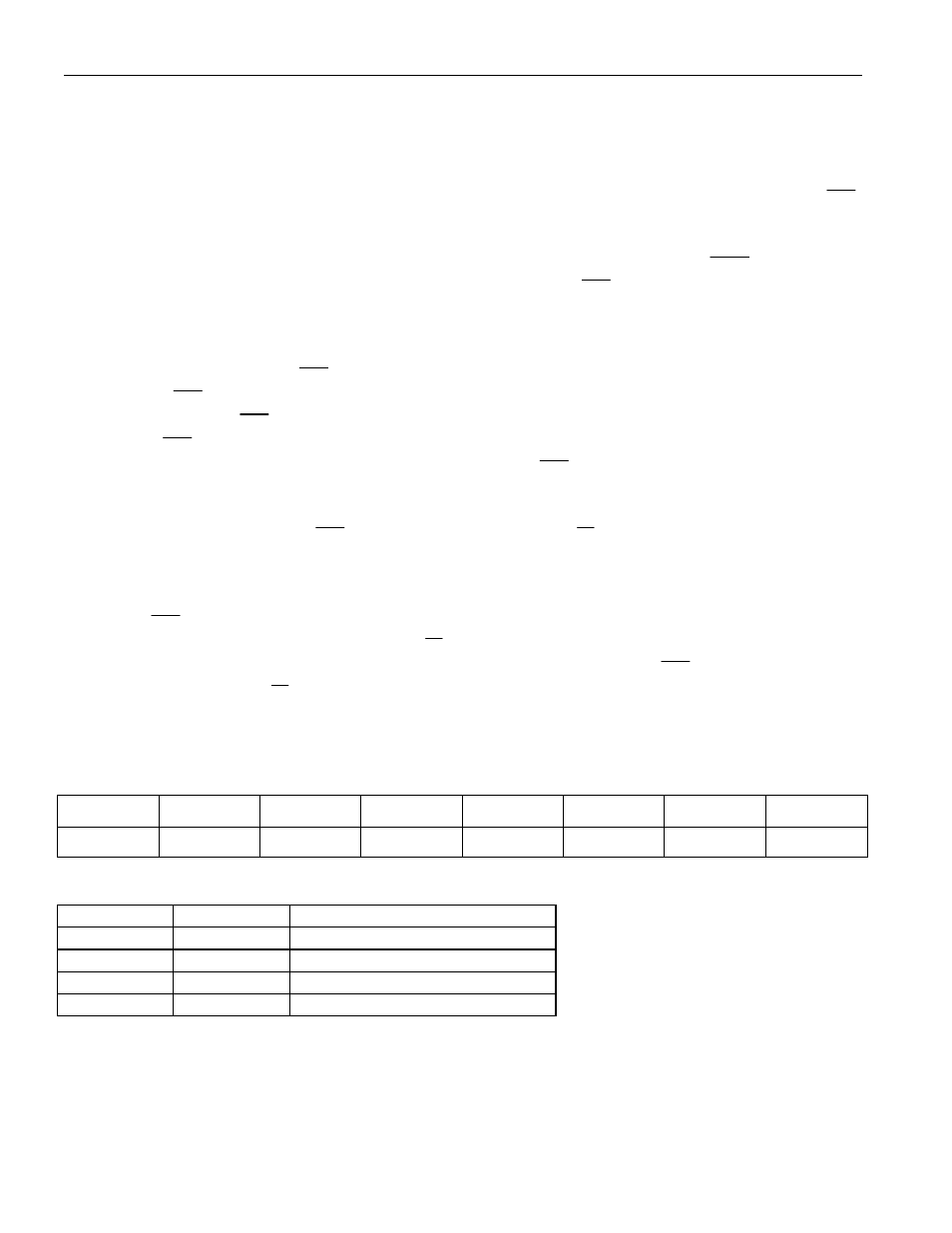

WATCHDOG REGISTER – 0Dh

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

0

0

0

0

0

TD1

TD0

WATCHDOG TIME-OUT BITS Table 2

TD1

TD0

WATCHDOG TIME-OUT

0

0

Watchdog Disabled

0

1

250ms

1

0

500ms

1

1

1000ms